ADSP-21368 SHARC Processor Hardware Reference 7-7

Input Data Port

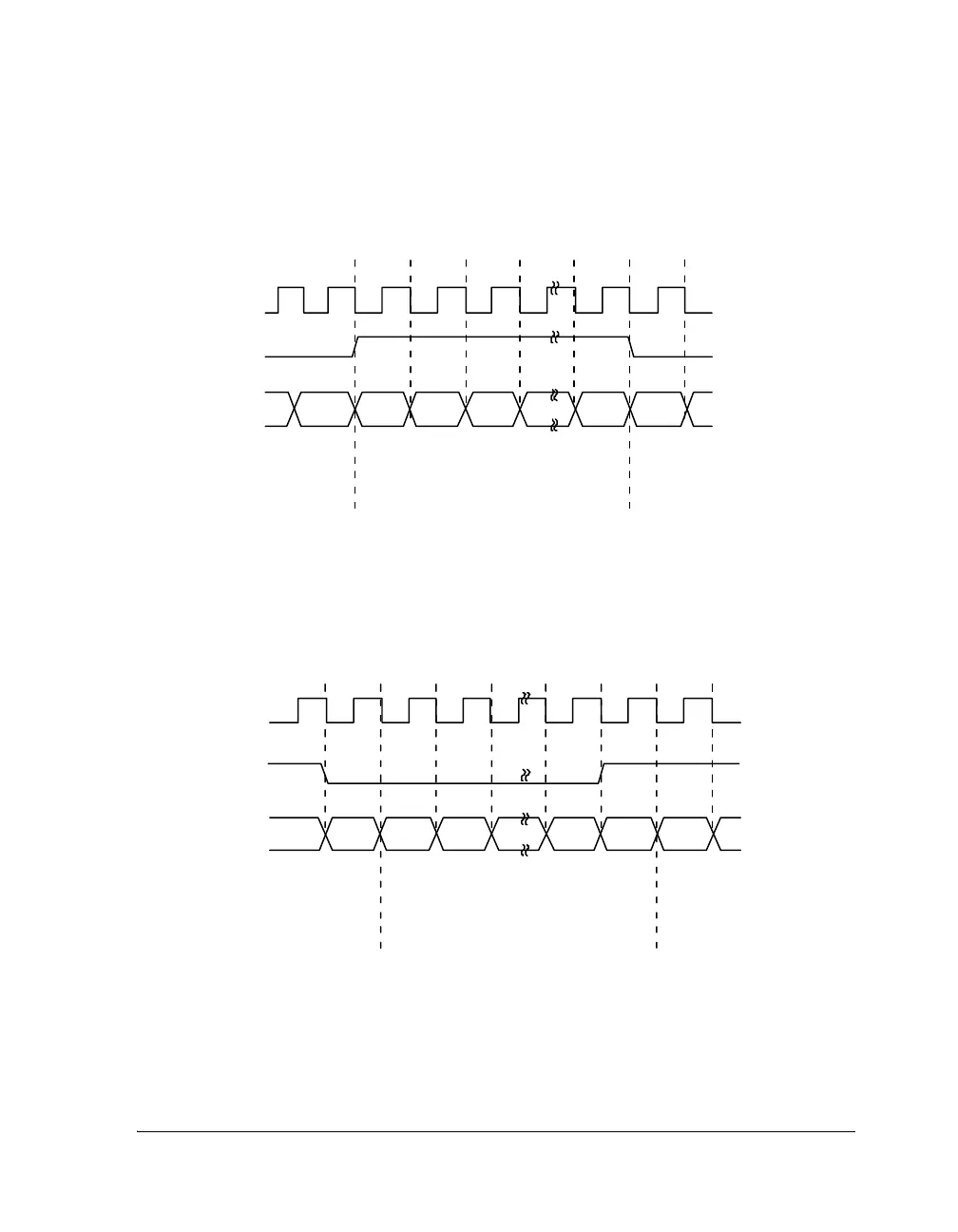

Figure 7-10 shows the relationship between frame sync, serial clock, and

left-justified sample pair data.

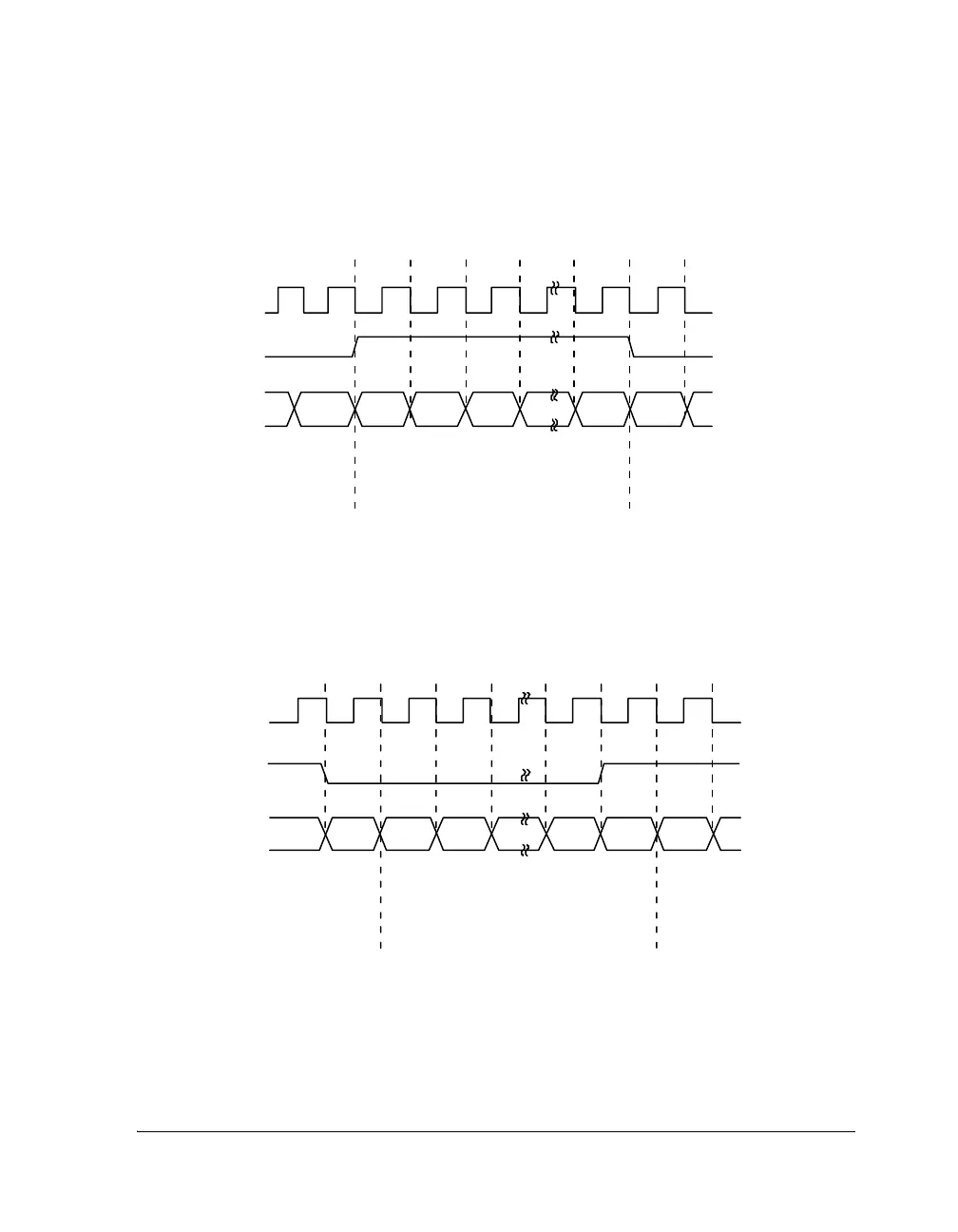

Figure 7-11 shows the relationship between frame sync, serial clock, and

I

2

S data.

Figure 7-10. Timing in Left-justified Sample Pair Mode

Figure 7-11. Timing in I

2

S Mode

SERIAL CLOCK

IDPx_CLK_I

FRAME SYNC (L/R)

IDPx_FS_I

LEFT-JUSTIFIED

SAMPLE PAI R

SERIAL DATA

IDPx_DAT_I

MSB

n

FRAME [n] FRAME [n]

LS B

n

MSB

n

FRAME [n-1]

LSB

n-1

RIGHT LEFT

RIGHT

06362 3261 31

SERIAL CLOCK

IDPx_CLK_I

FRAME SYNC (L/R)

IDPx_FS_I

I

2

S SERIAL DATA

IDPx_DAT_I

MSB

n

FRAME [n] FRAME [n]

LSB

n

MS B

n

FRAME [n-1]

LSB

n-1

06362 323133

RIGHT LEFT RIGHT

Loading...

Loading...