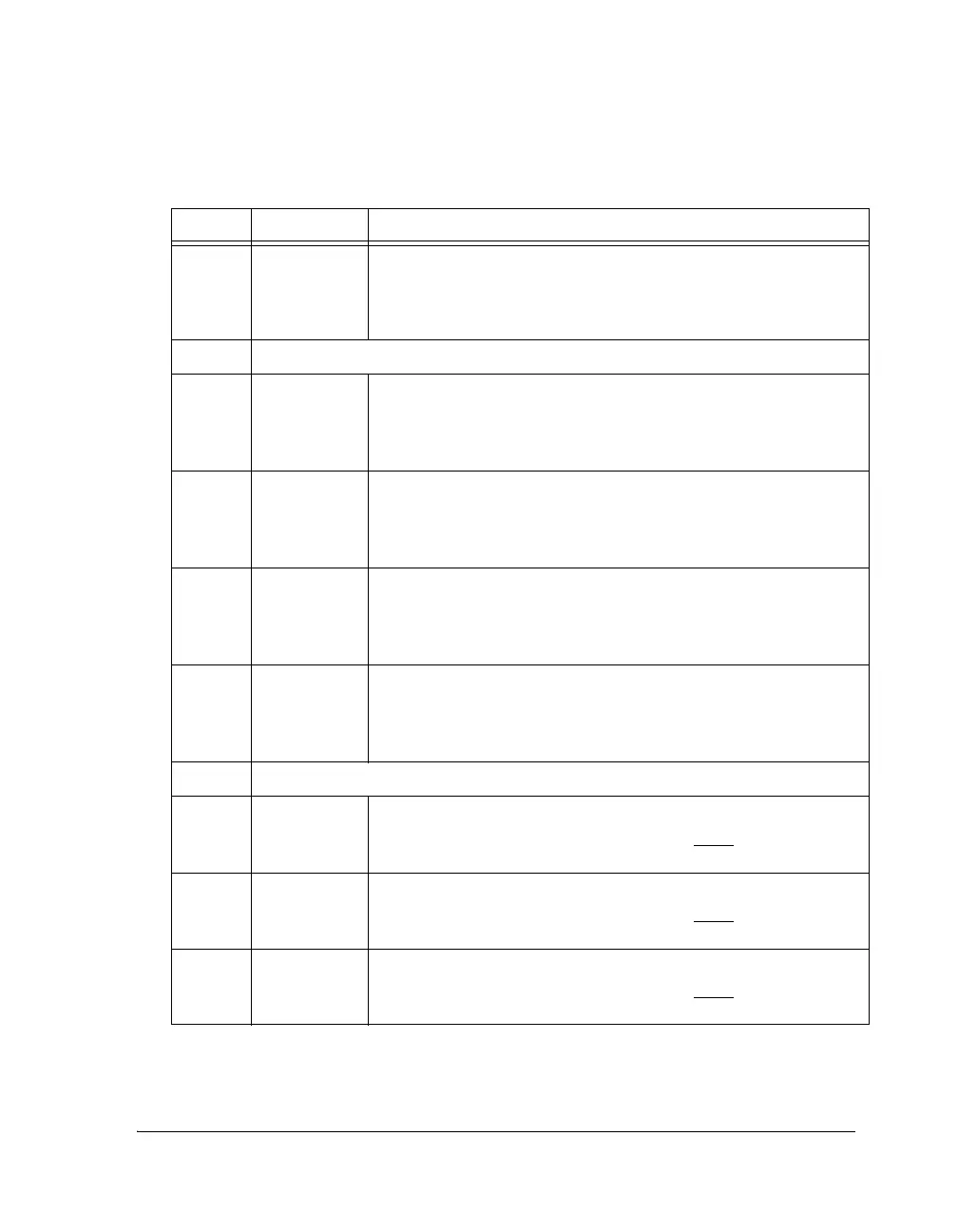

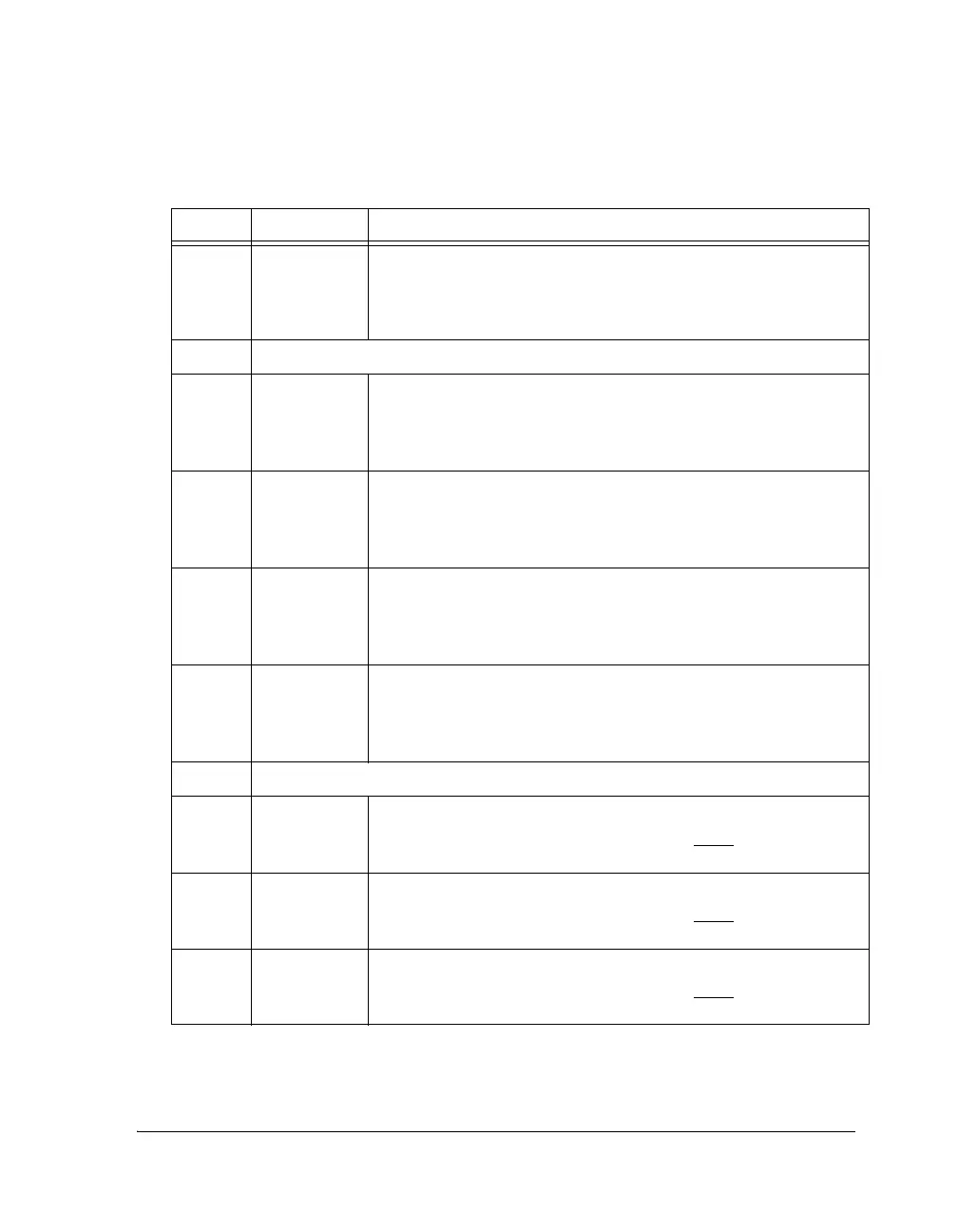

ADSP-21368 SHARC Processor Hardware Reference A-7

Register Reference

7 RBPR Rotating Priority Bus Arbitration. This bit enables or disables prior-

ity rotation among DMA channels. Permits core writes.

0 = Arbiter uses fixed priority

1 = Arbiter uses rotating priority

8Reserved

9IMDW0Internal Memory Data Width 0. Selects the data access size for inter-

nal memory block0 as 48- or 32-bit data. Permits core writes.

0 = Data bus width is 32 bits

1 = Data bus width is 48 bits

10 IMDW1 Internal Memory Data Width 1. Selects the data access size for inter-

nal memory block1 as 48- or 32-bit data. Permits core writes.

0 = Data bus width is 32 bits

1 = Data bus width is 48 bits

11 IMDW2 Internal Memory Data Width 2. Selects the data access size for inter-

nal memory block2 as 48- or 32-bit data. Permits core writes.

0 = Data bus width is 32 bits

1 = Data bus width is 48 bits

12 IMDW3 Internal Memory Data Width 3. Selects the data access size for inter-

nal memory block3 as 48- or 32-bit data. Permits core writes.

0 = Data bus width is 32 bits

1 = Data bus width is 48 bits

15-13 Reserved

16 IRQ0EN Flag0 Interrupt Mode.

0 = Flag0 pin is a general-purpose I/O pin. Permits core writes.

1 = Flag0 pin is allocated to interrupt request IRQ0

.

17 IRQ1EN Flag1 Interrupt Mode.

0 = Flag1 pin is a general-purpose I/O pin. Permits core writes.

1 = Flag1 pin is allocated to interrupt request IRQ1

.

18 IRQ2EN Flag2 Interrupt Mode.

0 = Flag2 pin is a genera-purpose I/O pin. Permits core writes.

1 = Flag2 pin is allocated to interrupt request IRQ2

.

Table A-1. SYSCTL Register Bit Descriptions (Cont’d)

Bit Name Description

Loading...

Loading...