ADSP-21368 SHARC Processor Hardware Reference A-101

Register Reference

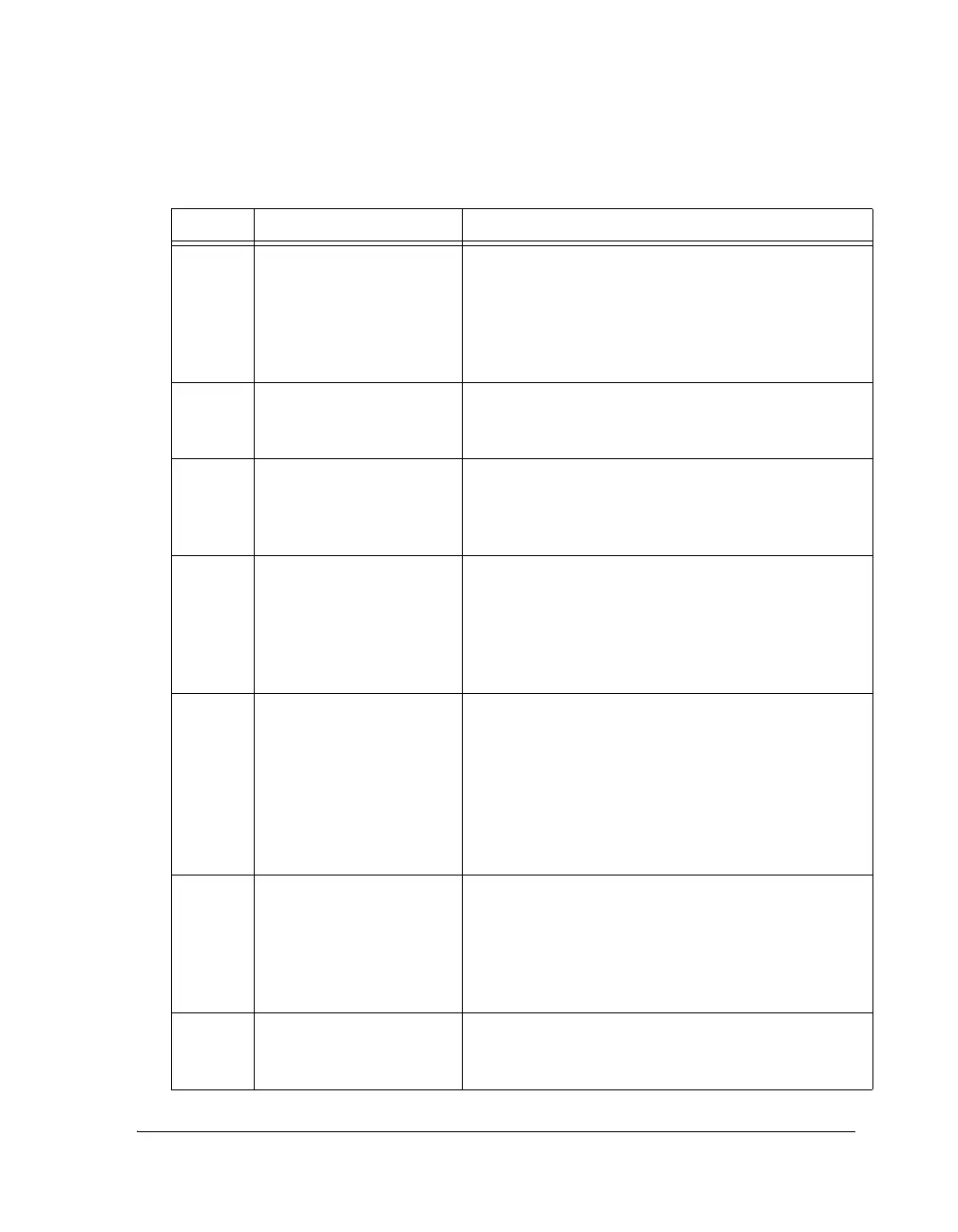

23–22 SRC1_DEEMPHASIS De-emphasis Filter Select. Enables deemphasis on

incoming audio data for SRC 1.

00 = No de-emphasis

01 = 33 kHz

10 = 44.1 kHz

11 = 48 kHz

24 SRC1_SOFTMUTE Soft Mute. Enables soft mute on SRC 1.

0 = No mute

1 = Mute (default)

25 SRC1_DITHER Dither Select. Disables dithering on SRC 1 when a word

length less than 24 bits is selected.

0 = Dithering is disabled (default)

1 = Dithering is enabled

27–26 SRC1_SMODEOUT Serial Output Format. Selects the serial output format

for SRC 1 as follows.

00 = Left-justified (default)

01 = I

2

S

10 = TDM mode

11 = Right-justified

29–28 SRC1_LENOUT Output Word Length Select. Selects the serial output

word length for SRC 1 as follows.

00 = 24 bits

01 = 20 bits

10 = 18 bits

11 = 16 bits

Any word length less than 24 bits will have dither added

to the unused LSBs if SRCx_DITHER is enabled (= 1).

30 SRC1_MPHASE Match-Phase Mode Select. Configures the SRC 1 mod-

ules to not use their own internally-generated sample rate

ratio but use an externally-generated ratio. Used with

TDM data.

0 = Matched-phase disabled (default)

1 = Matched-phase enabled

31 SRC1_ENABLE SRC Enable. Enables SRC 1.

0 = Disabled

1 = Enabled

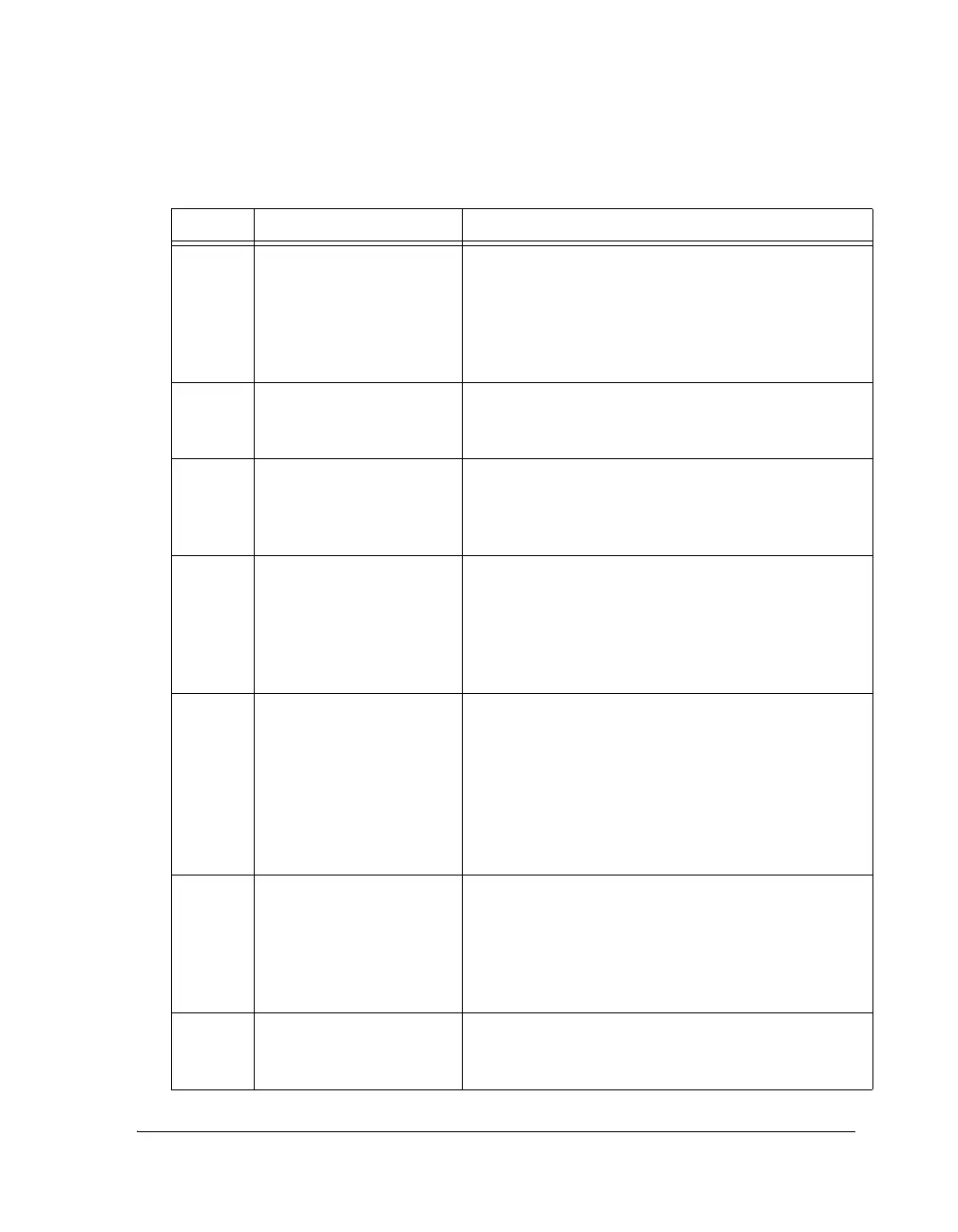

Table A-42. SRCCTL0 Register Bit Descriptions (Cont’d)

Bit Name Description

Loading...

Loading...