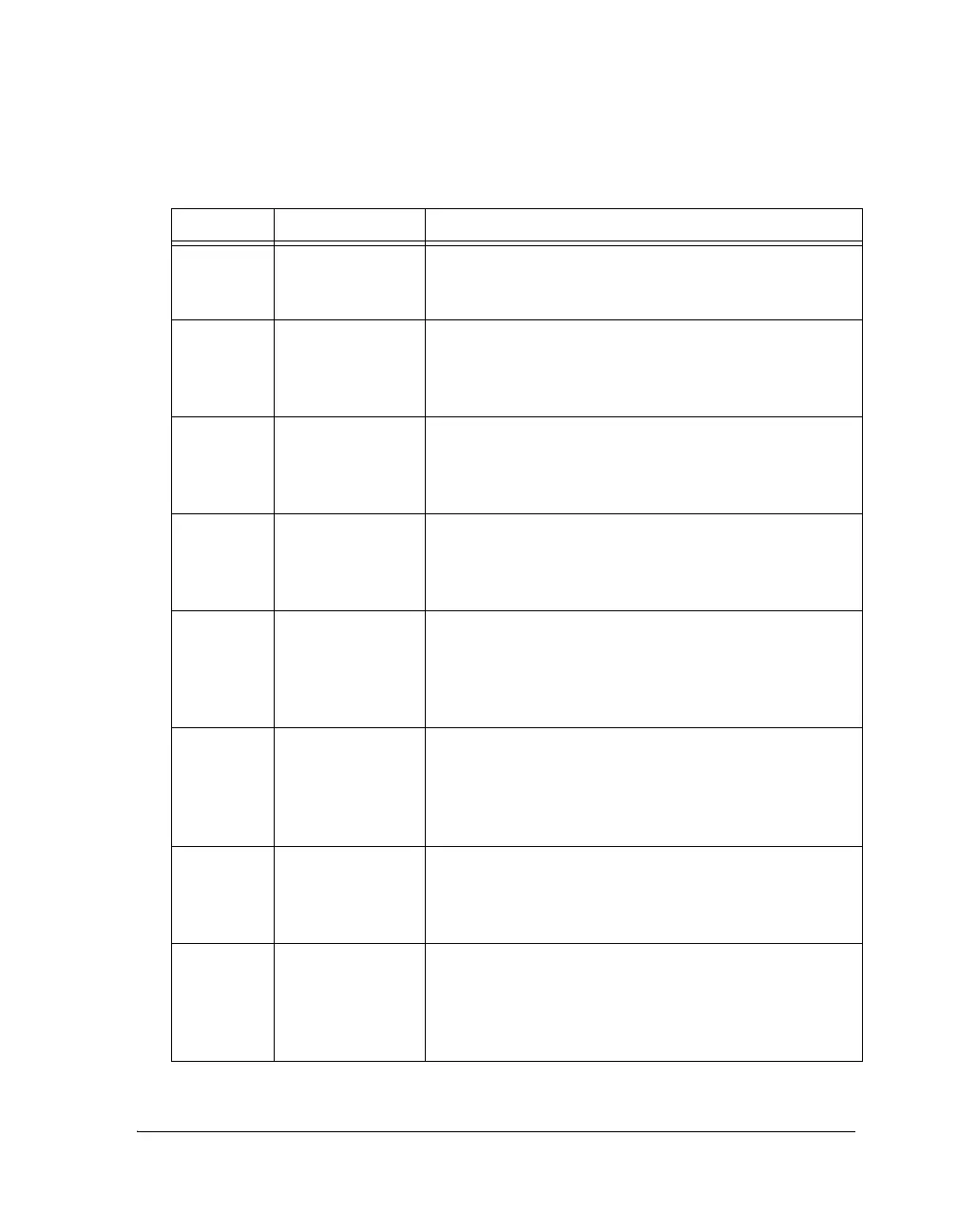

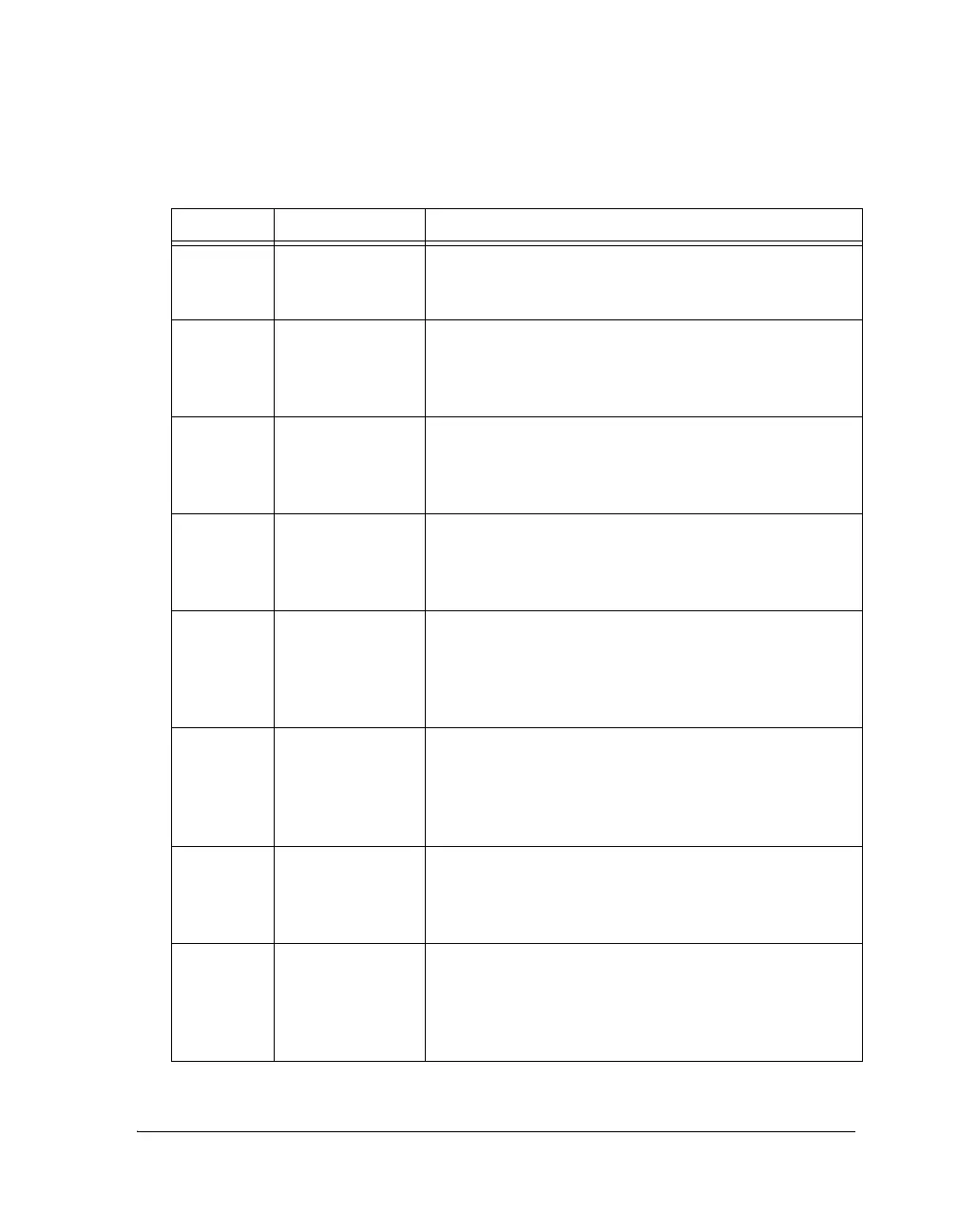

ADSP-21368 SHARC Processor Hardware Reference B-11

Interrupts

19 P18IMSK

(SPIBMSK)

Programmable Interrupt Mask 18 (SPI Interrupt Mask Sec-

ondary SPI Port). Unmasks the SPIB interrupt (if set, = 1),

or masks the SPIB interrupt (if cleared, = 0).

20 P6IMSKP

(SP0IMSKP)

Programmable Interrupt Mask Pointer 9 (SPORT0 Inter-

rupt Mask Pointer). When the processor is servicing another

interrupt, this bit indicates if the SP0I interrupt is unmasked

(if set, = 1), or the SP0I interrupt is masked (if cleared, = 0).

21 P7IMSKP

(SP2IMSKP)

Programmable Interrupt Mask Pointer 7 (SPORT2 Inter-

rupt Mask Pointer). When the processor is servicing another

interrupt, this bit indicates if the SP2I interrupt is unmasked

(if set, = 1), or the SP2I interrupt is masked (if cleared, = 0).

22 P8IMSKP

(SP4IMSKP)

Programmable Interrupt Mask Pointer 8 (SPORT4 Inter-

rupt Mask Pointer). When the processor is servicing another

interrupt, this bit indicates if the SP4I interrupt is unmasked

(if set, = 1), or the SP4I interrupt is masked (if cleared, = 0).

23 P9IMSKP

(EPDMA0IMSKP)

Programmable Interrupt Mask Pointer 9 (External Port

DMA Channel 0 Interrupt Mask Pointer). When the pro-

cessor is servicing another interrupt, this bit indicates if the

EPDMA0 interrupt is unmasked (if set, = 1), or masked (if

cleared, = 0).

24 P10IMSKP

(GPTMR1MSKP)

Programmable Interrupt Mask Pointer 10 (General-Pur-

pose IOP Timer 1 Interrupt Mask Pointer).

When the processor is servicing another interrupt, this bit

indicates if the GPTMR1I interrupt is unmasked (if set, = 1),

or the GPTMR1I interrupt is masked (if cleared, = 0).

25 P11MSKP Programmable Interrupt Mask Pointer 11 (SPORT7 Inter-

rupt Mask Pointer). When the processor is servicing another

interrupt, this bit indicates if the SP7I interrupt is unmasked

(if set, = 1), or the SP7I interrupt is masked (if cleared, = 0).

26 P12IMSKP

(DAI2IMSKP)

Programmable Interrupt Mask Pointer 12 (DAI Low Prior-

ity Interrupt Mask Pointer).

When the processor is servicing another interrupt, this bit

indicates if the DAI2I is unmasked (if set, = 1), or masked (if

cleared, = 0).

Table B-4. LIRPTL Register Bit Descriptions (Cont’d)

Bit Name Description

Loading...

Loading...