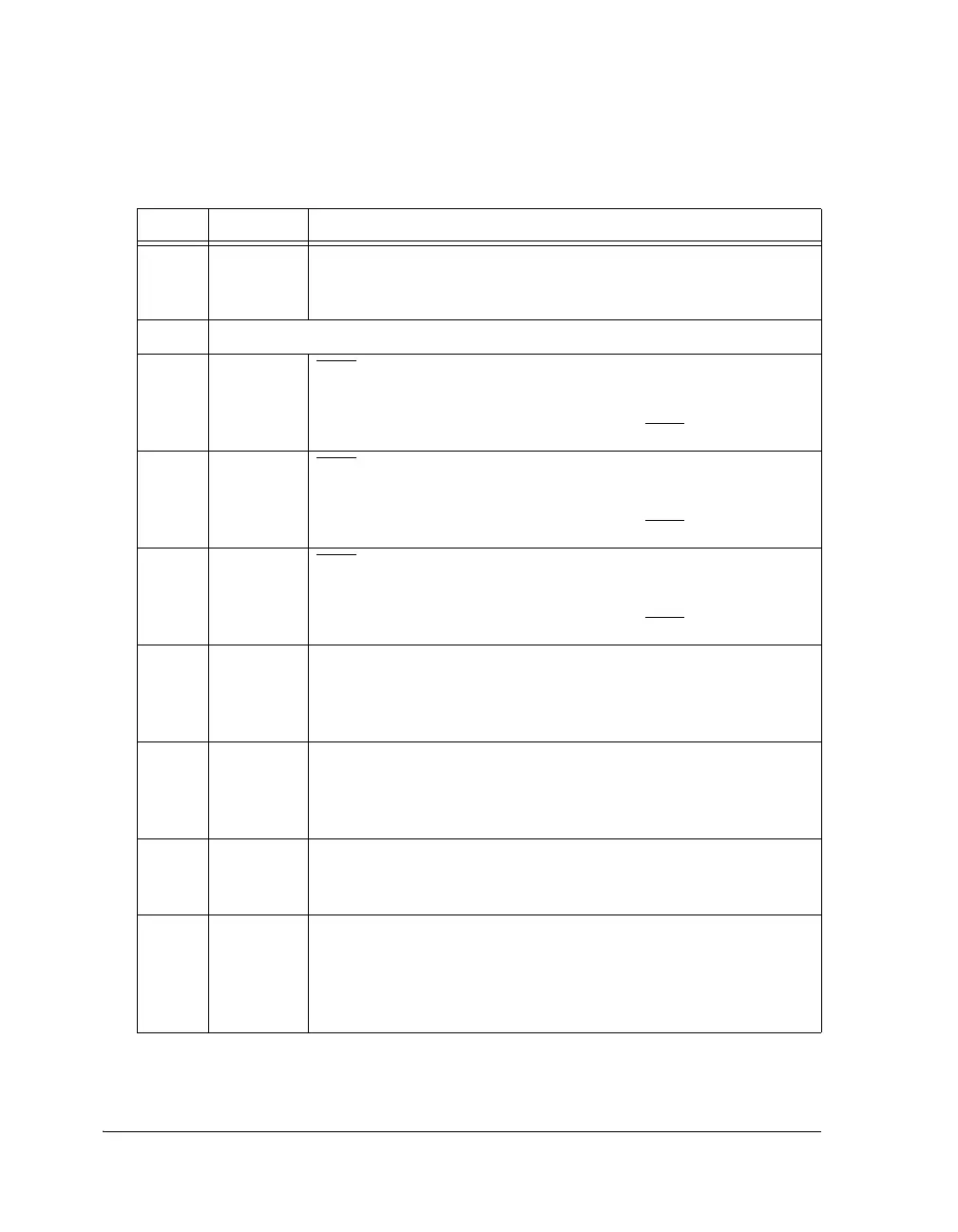

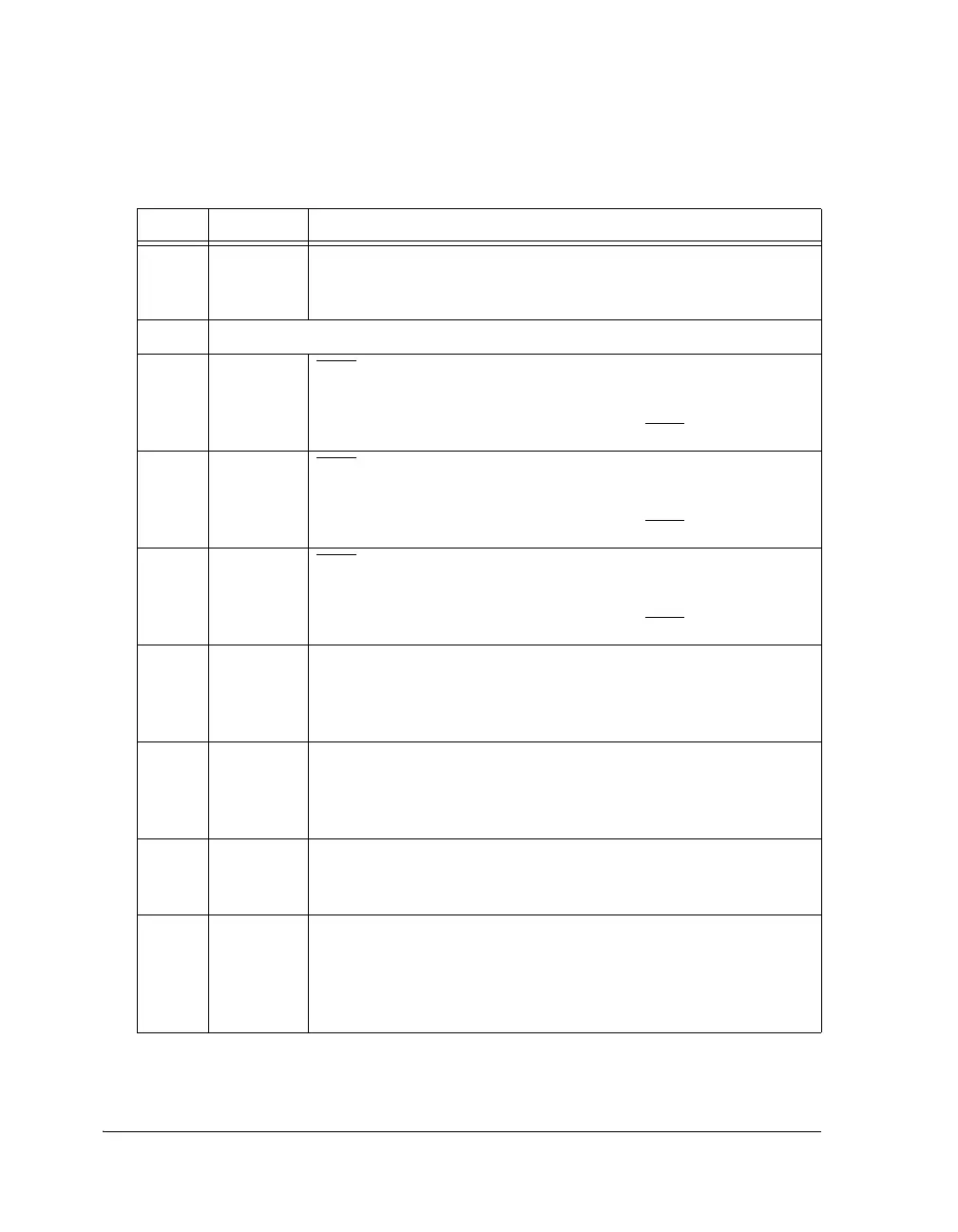

Interrupt Registers

B-24 ADSP-21368 SHARC Processor Hardware Reference

6BKPIHardware Breakpoint Interrupt. When the processor is servicing

another interrupt, this bit indicates if the BKPI interrupt is unmasked

(if set, = 1), or masked (if cleared, = 0).

7Reserved

8IRQ2IIRQ2 Hardware Interrupt. When the processor is servicing another

interrupt, this bit indicates if the IRQ2I interrupt is unmasked

(if set, = 1), or masked (if cleared, = 0). An IRQ2I occurs when an exter-

nal device asserts the FLAG2 pin configured as IRQ2

.

9IRQ1IIRQ1 Hardware Interrupt. When the processor is servicing another

interrupt, this bit indicates if the IRQ1I interrupt is unmasked

(if set, = 1), or masked (if cleared, = 0). An IRQ1I occurs when an exter-

nal device asserts the FLAG1 pin configured as IRQ1

.

10 IRQ0I IRQ0 Hardware Interrupt. When the processor is servicing another

interrupt, this bit indicates if the IRQ0I interrupt is unmasked

(if set, = 1), or masked (if cleared, = 0). An IRQ0I occurs when an exter-

nal device asserts the FLAG0 pin configured as IRQ0

.

11 DAI1I DAI High Priority Interrupt. When the processor is servicing another

interrupt, this bit indicates if the DAI1I interrupt is unmasked

(if set, = 1), or masked (if cleared, = 0). This is the higher priority

option.

12 SPIAI SPI Transmit or Receive High Priority Interrupt. When the processor

is servicing another interrupt, this bit indicates if the SPIAI interrupt is

unmasked (if set, = 1), or the SPIAI interrupt is masked (if cleared, = 0).

This is the higher priority option.

13 GPTMR0I General-Purpose IOP Timer 0 Interrupt. When the processor is servic-

ing another interrupt, this bit indicates if the GPTMR0I interrupt is

unmasked (if set, = 1), or masked (if cleared, = 0).

14 SP1I SPORT 1 Interrupt. When the processor is servicing another interrupt,

this bit indicates if the SP1I interrupt is unmasked (if set, = 1), or

masked (if cleared, = 0). An SP1I interrupt occurs two cycles after the

last bit of an input/output serial word is latched into/from

RXSP1A/TXSP1A, or RXSP1B/TXSP1B.

Table B-7. IMASKP Register Bit Descriptions (Cont’d)

Bit Name Description

Loading...

Loading...