R01UH0823EJ0100 Rev.1.00 Page 1137 of 1823

Jul 31, 2019

RX23W Group 35. I

2

C-bus Interface (RIICa)

[Setting conditions]

When master arbitration-lost detection is enabled: ICFER.MALE = 1

When the internal SDA output state does not match the SDA0 line level at the rising edge of SCL clock except for

the ACK period during data (including slave address) transmission in master transmit mode (when the SDA0 line is

driven low while the internal SDA output is at a high level (the SDA0 pin is in the high-impedance state))

When a start condition is detected while the ICCR2.ST bit is 1 (start condition issuance request) or the internal SDA

output state does not match the SDA0 line level

When the ICCR2.ST bit is set to 1 (start condition issuance request) with the ICCR2.BBSY flag set to 1.

When NACK arbitration-lost detection is enabled: ICFER.NALE = 1

When the internal SDA output state does not match the SDA0 line level at the rising edge of SCL clock in the ACK

period during NACK transmission in receive mode

When slave arbitration-lost detection is enabled: ICFER.SALE = 1

When the internal SDA output state does not match the SDA0 line level at the rising edge of SCL clock except for

the ACK period during data transmission in slave transmit mode

[Clearing conditions]

When 0 is written to the AL flag after reading AL = 1

When 1 is written to the ICCR1.IICRST bit to apply an RIIC reset or an internal reset

×: Don’t care

START Flag (Start Condition Detection Flag)

[Setting condition]

When a start condition (or a restart condition) is detected

[Clearing conditions]

When 0 is written to the START bit after reading START = 1

When a stop condition is detected

When 1 is written to the ICCR1.IICRST bit to apply an RIIC reset or an internal reset

STOP Flag (Stop Condition Detection Flag)

[Setting condition]

When a stop condition is detected

[Clearing conditions]

When 0 is written to the STOP bit after reading STOP = 1

When 1 is written to the ICCR1.IICRST bit to apply an RIIC reset or an internal reset

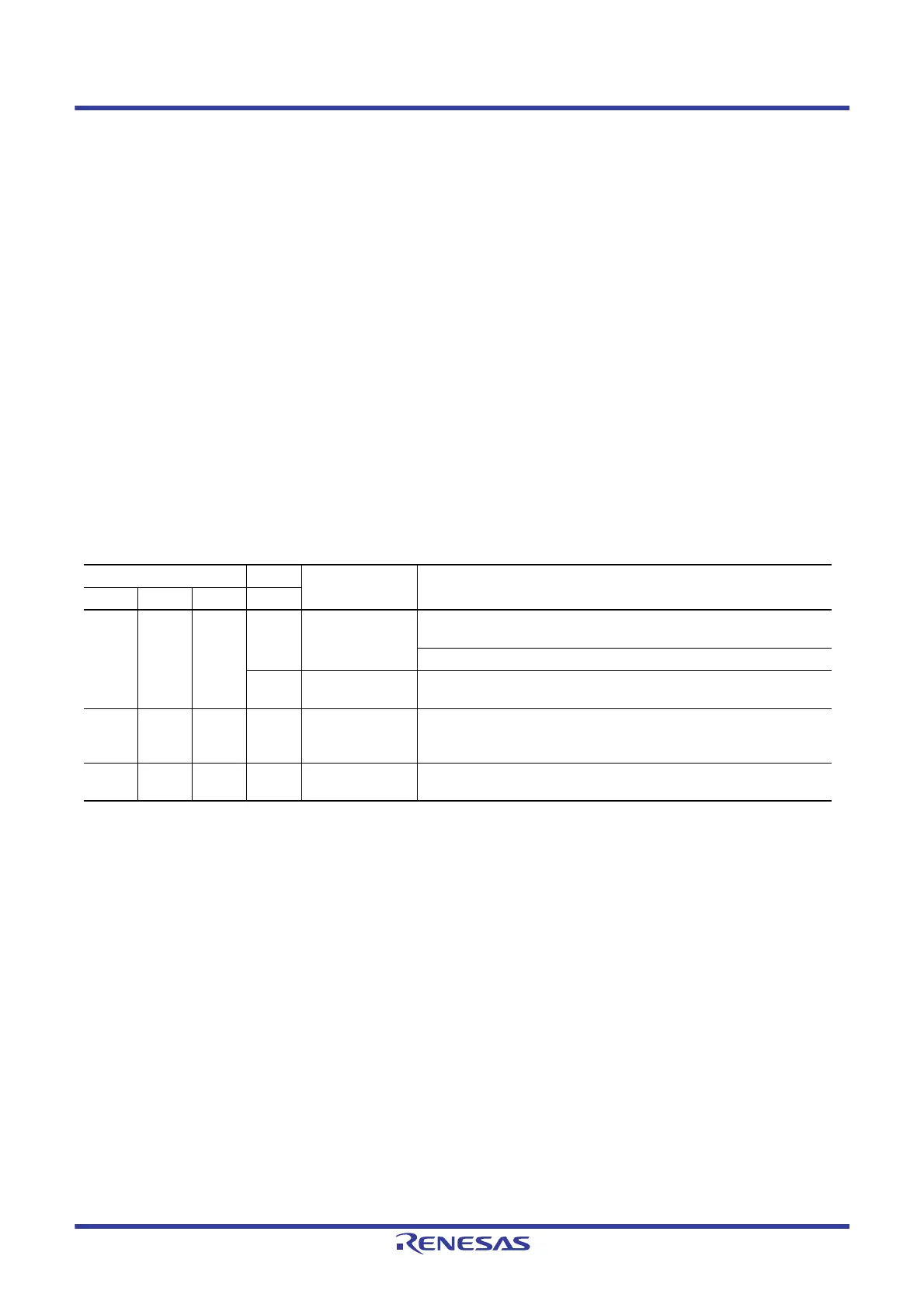

Table 35.4 Relationship between Arbitration-Lost Generation Sources and Arbitration-Lost Enable Functions

ICFER ICSR2

Error Arbitration-Lost Generation SourceMALE NALE SALE AL

1 × × 1 Start condition

issuance error

When internal SDA output state does not match SDA0 line level when a

start condition is detected while the ICCR2.ST bit is 1

When ICCR2.ST bit is set to 1 with ICCR2.BBSY flag set to 1

1 Transmit data

mismatch

When transmit data (including slave address) does not match the bus

state in master transmit mode

×1×1NACK

transmission

mismatch

When ACK is detected during transmission of NACK in master receive

mode or slave receive mode

× × 1 1 Transmit data

mismatch

When transmit data does not match the bus state in slave transmit mode

Loading...

Loading...