R01UH0823EJ0100 Rev.1.00 Page 1149 of 1823

Jul 31, 2019

RX23W Group 35. I

2

C-bus Interface (RIICa)

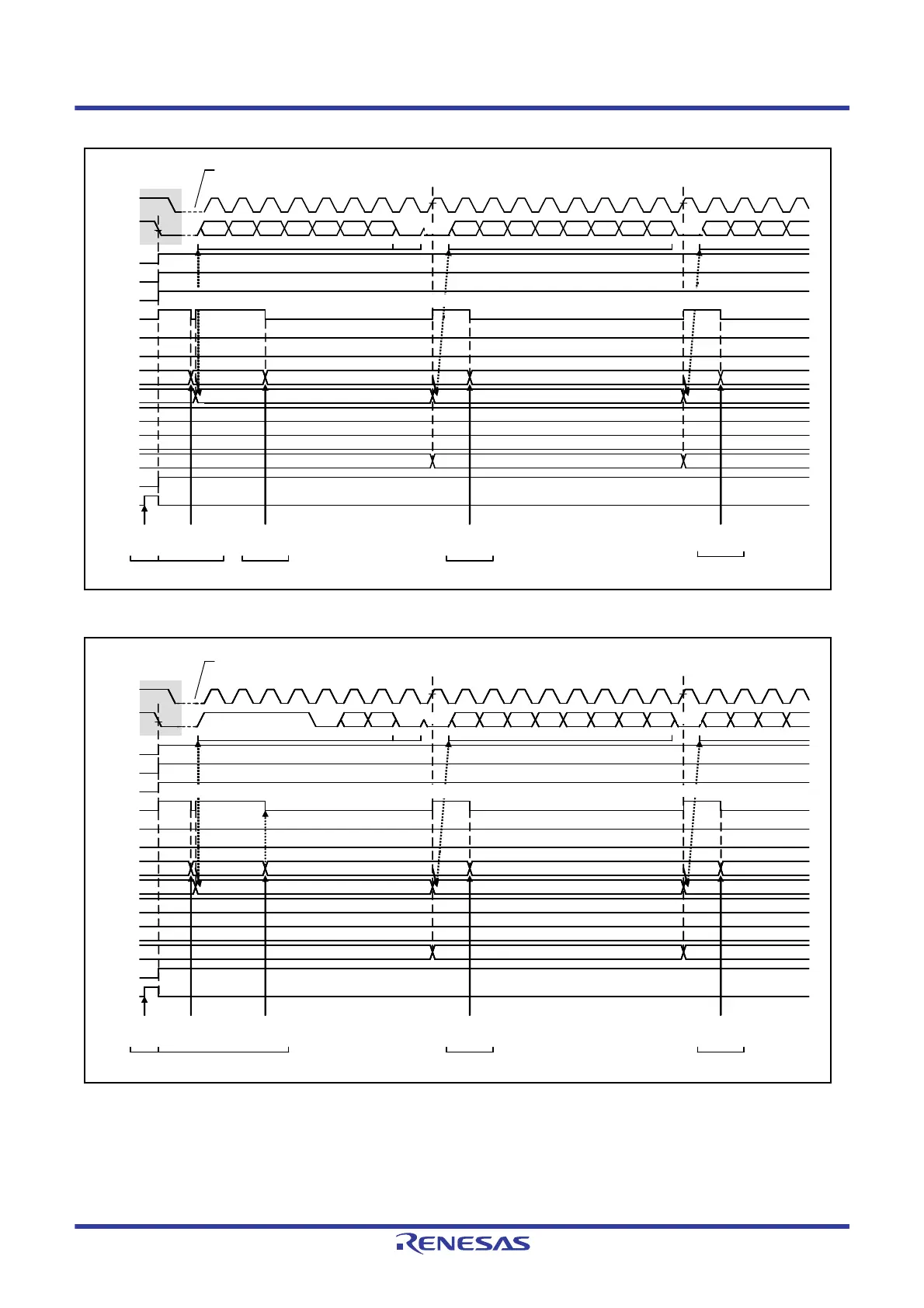

Figure 35.7 Master Transmit Operation Timing (1) (7-Bit Address Format)

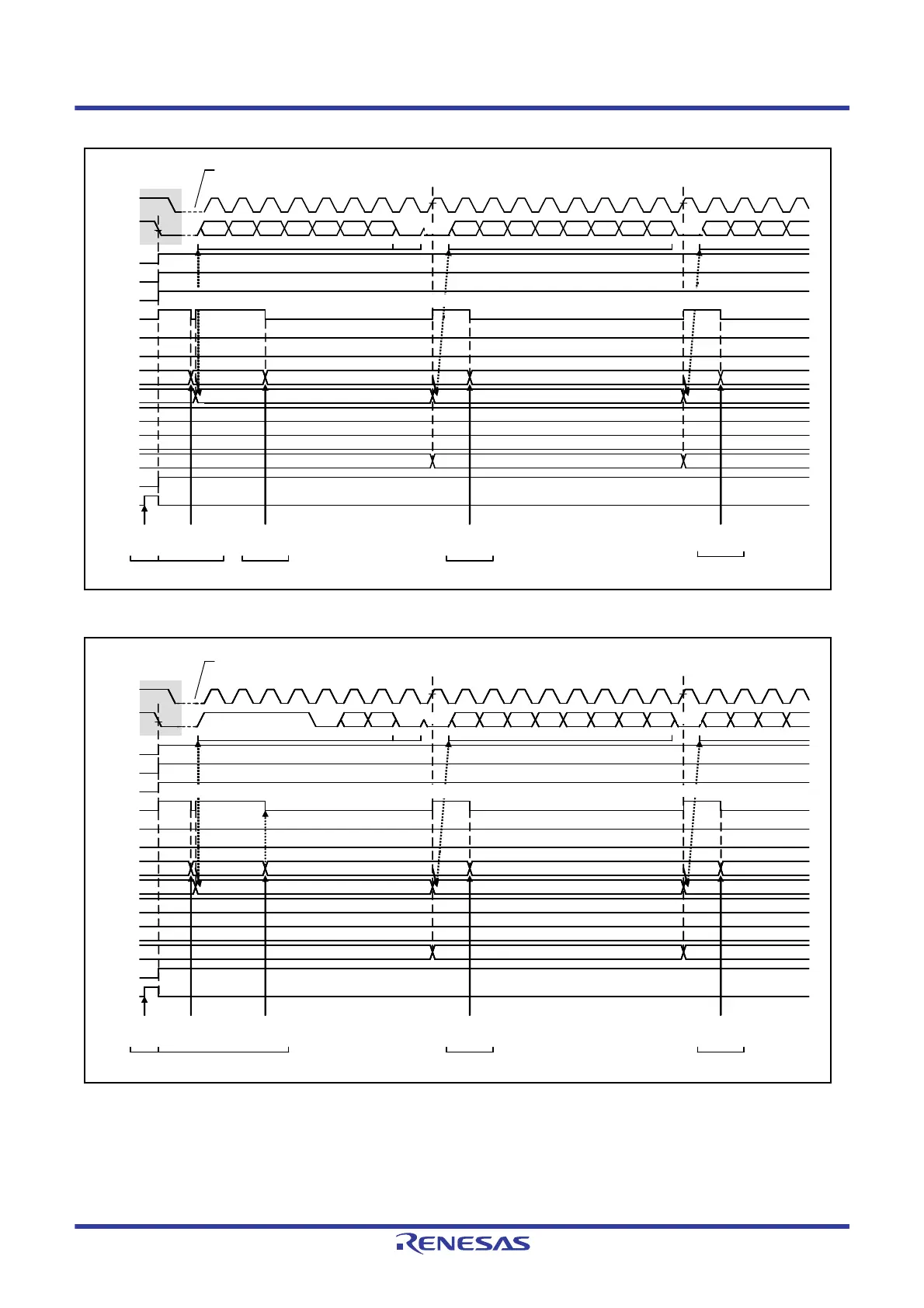

Figure 35.8 Master Transmit Operation Timing (2) (10-Bit Address Format)

Write data to

ICDRT register

(7-bit address + W)

Write data to

ICDRT register

(DATA 1)

Write data to

ICDRT register

(DATA 2)

7-bit address + W

Transmit data (DATA 2)Transmit data (7-bit address + W)

TDRE

MST

TRS

BBSY

TEND

S 9

Write data to

ICDRT register

(DATA 3)

8

b0

ST

START

ICDRT

ICDRS

7-bit address + W

DATA 1

DATA 1

DATA 2

DATA 3

DATA 2

Write 1

to ST bit

1

b7

7-bit slave address

W

2

b6

3

b5

4

b4

5

b3

6

b2

7

b1

2

b6

4

b4

5

b3

6

b2

7

b1

3

b5

8

b0

1

b7

2

b6

4

b4

3

b5

DATA 1 DATA 2

1

b7

RDRF

ICDRR

9

ACKBT

ACKBR

0(ACK)

X (ACK/NACK)

[3] [4]

[4]

[2] [4]

0(ACK)

ACK

ACK

0(ACK)

XXXX (Initial value/last data for reception)

Automatic low-hold (to prevent wrong transmission)

Transmit data (DATA 1)

Transmit data (upper 10 bits + W)

0 (ACK)

Write data to

ICDRT register

(11110b + 2

bits + W)

Write data to

ICDRT register

(lower 8 bits)

Write data to

ICDRT register

(DATA 1)

Write data to

ICDRT register

(DATA 2)

Write 1

to ST bit

RDRF

ICDRR

TDRE

MST

TRS

BBSY

TEND

S 9

ST

START

ICDRT

ICDRS

Upper 10 bits + W

Lower 10 bits

Lower 10 bits

DATA 1

DATA 2

DATA 1

Upper 10-bit addresses (11110b + 2 bits)

W

Lower 10-bit addresses

1

b7

2

b6

4

b4

5

b3

6

b2

7

b1

3

b5

8

b0

1

b7

2

b6

4

b4

3

b5

DATA 1

2

b6

3

b5

4

b4

5

b3

6

b2

8

b0

7

b1

1

b7

9

ACKBT

ACKBR

[3] [4] [4][2]

X (ACK/NACK)

Transmit data (lower 10 bits)

ACK

Transmit data (DATA 1)

ACK

Automatic low-hold (to prevent wrong transmission)

10-bit address + W

0 (ACK) 0 (ACK)

XXXX (Initial value/last data for reception)

Loading...

Loading...