R01UH0823EJ0100 Rev.1.00 Page 1158 of 1823

Jul 31, 2019

RX23W Group 35. I

2

C-bus Interface (RIICa)

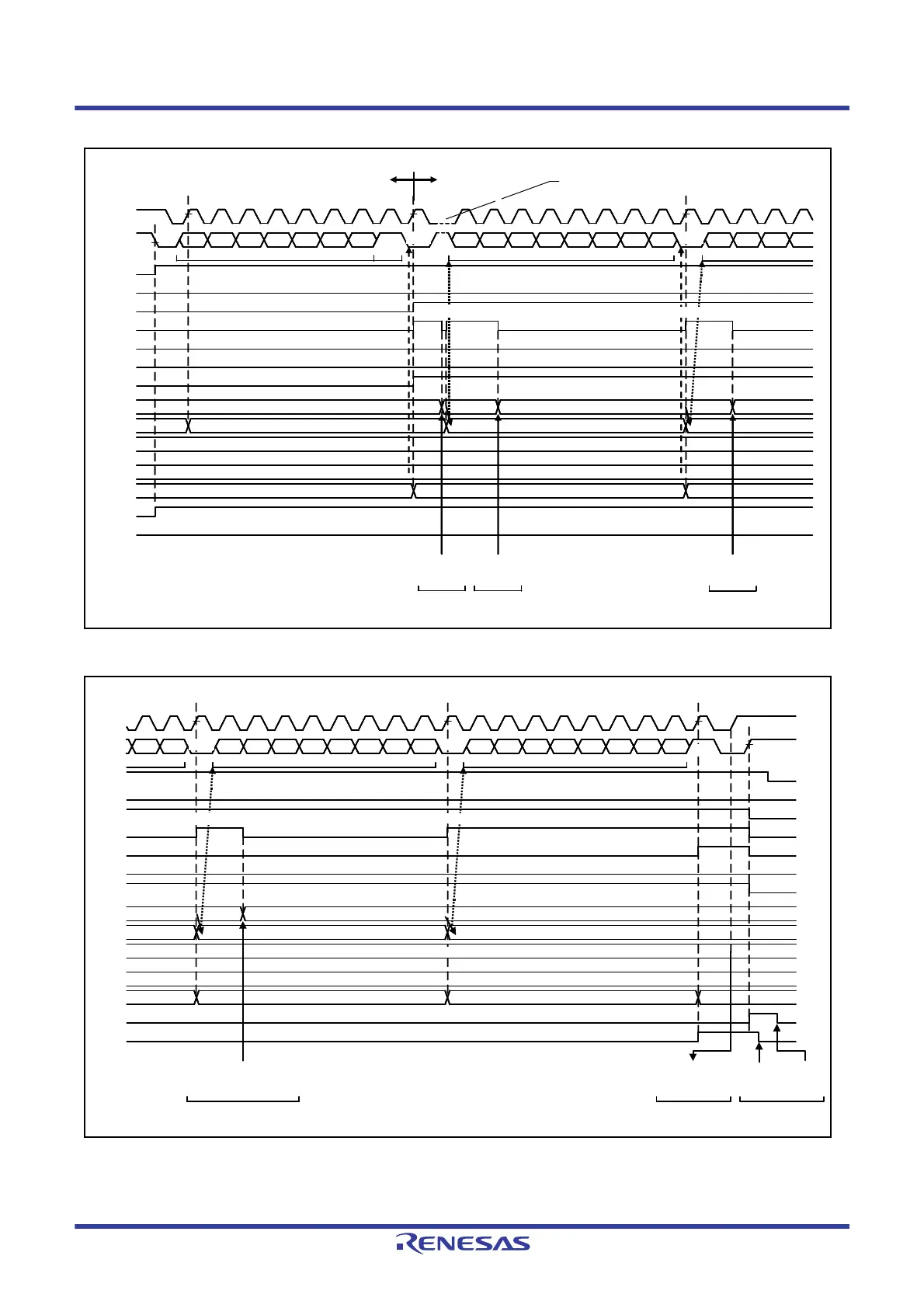

Figure 35.16 Slave Transmit Operation Timing (1) (7-Bit Address Format)

Figure 35.17 Slave Transmit Operation Timing (2)

Automatic low hold (to prevent wrong transmission)

0(ACK)

Write data to

ICDRT register

(DATA 1)

TDRE

MST

TRS

BBSY

TEND

S 9

NACKF

START

ICDRT

ICDRS

DATA 2 DATA 3

DATA 2

7-bit slave address R

2

b6

3

b5

4

b4

5

b3

6

b2

7

b1

2

b6

4

b4

5

b3

6

b2

7

b1

3

b5

8

b0

1

b7

2

b6

4

b4

3

b5

DATA 1 DATA 2

RDRF

ICDRR

ACKBT

ACKBR

[3] [3]

1

b7

98

b0

DATA 1

DATA 1

[3]

1

b7

Slave receive mode Slave transmit mode

AASy

XXXX (Initial value/last data for transmission)

7-bit address + R

XXXX (Initial value/last data for reception)

0 (ACK)

X(ACK/NACK) 0(ACK)

Write data to

ICDRT register

(DATA 2)

Write data to

ICDRT register

(DATA 3)

ACKACK

Transmit data (DATA 2)

Transmit data (DATA 1)

ACK

TDRE

MST

TRS

BBSY

TEND

STOP

ICDRT

ICDRS

DATA n

DATA n

2

b6

4

b4

5

b3

6

b2

7

b1

3

b5

8

b0

1

b7

2

b6

4

b4

5

b3

6

b2

7

b1

3

b5

8

b0

8

b0

1

b7

7

b1

DATA n-1

DATA n-1 DATA nDATA n-2

RDRF

ICDRR

99

ACKBT

ACKBR

[5][4]

NACKF

9 P

[7]

AASy

DATA n-2 DATA n-1

0(ACK)

1 (NACK)

ACK

NACK

Transmit data (DATA n-1) Transmit data (DATA n)

XXXX (Initial value/last data for reception)

Write data to ICDRT register

(last data for transmission

[DATA n])

Clear

STOP

flag

Clear

NACKF flag

0(ACK)

0(ACK)

SCL0

SDA0

Dummy read

ICDRR register

(SCL0 line is released)

Loading...

Loading...