R01UH0823EJ0100 Rev.1.00 Page 1321 of 1823

Jul 31, 2019

RX23W Group 37. Serial Sound Interface (SSI)

Transmitting and Receiving in the Order of Serial Data and Padding Bits; without Delay

Figure 37.12 Transmitting and Receiving in the Order of Serial Data and Padding Bits; without Delay

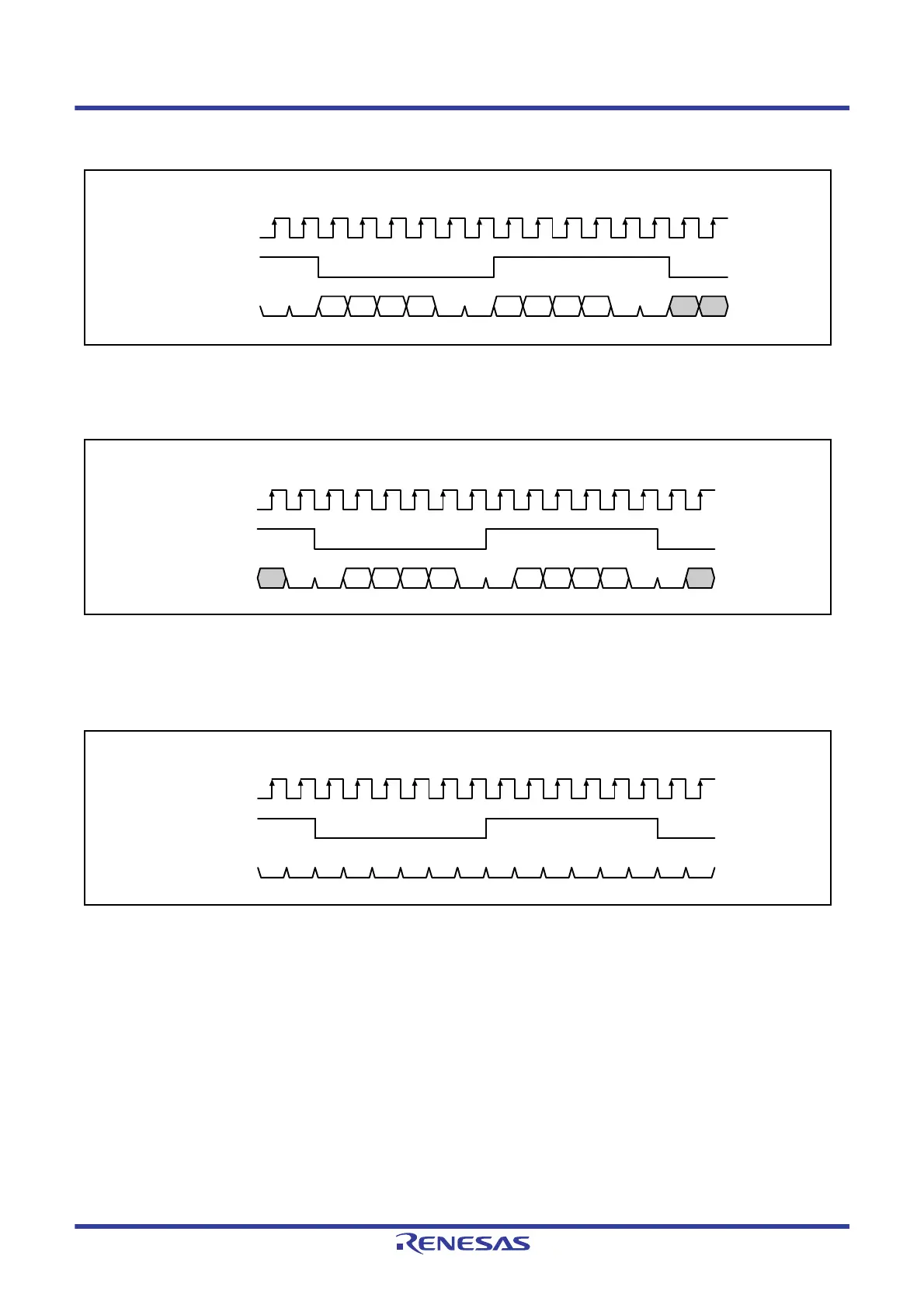

Parallel Right-Justified with Delay

Figure 37.13 Parallel Right-Justified with Delay

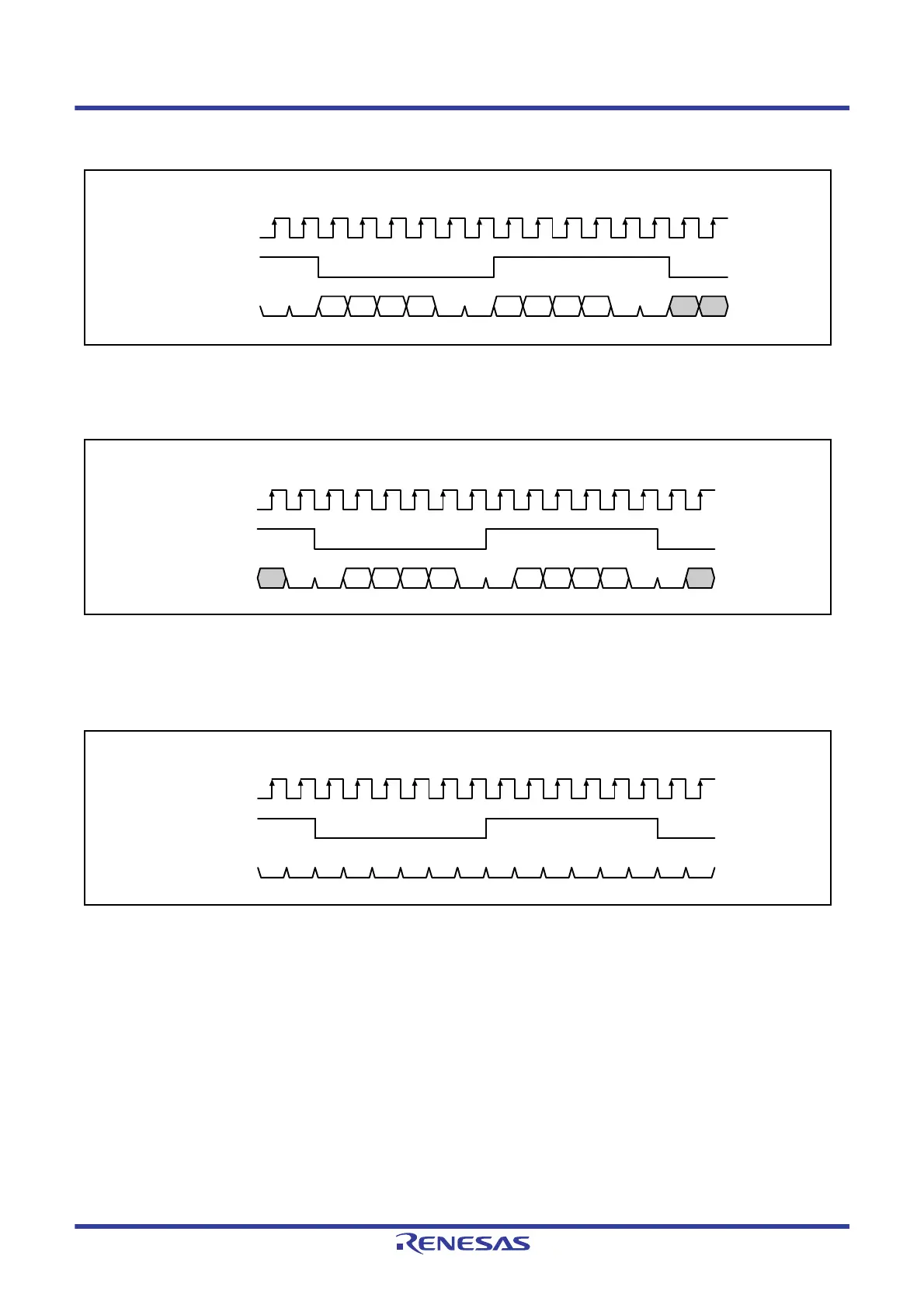

Mute Enabled

When the SSICR.MUEN bit is set to 1, the SSITXD0 pin becomes low (0) without synchronizing SSIWS0.

Figure 37.14 Mute Enabled

TD31

TD30

Same as basic format sample configuration except SSICR.DEL bit = 1

SSISCK

SSIWS

SSIDATA

System word 1 System word 2

00

TD31 TD30 TD29 TD28 0 0 TD31 TD30 TD29 TD28 0 0

TD3

TD0

Same as basic format sample configuration except SSICR.PDTA bit = 1

SSISCK

SSIWS

SSIDATA

System word 1 System word 2

00

TD3 TD2 TD1 TD0 0 0 TD3 TD2 TD1 TD0 0 0

Same as basic format sample configuration except SSICR.MUEN bit = 1 (TD data ignored)

SSISCK

SSIWS

SSIDATA

System word 1 System word 2

00

000000000000

0

0

Loading...

Loading...