R01UH0823EJ0100 Rev.1.00 Page 1595 of 1823

Jul 31, 2019

RX23W Group 44. 12-Bit A/D Converter (S12ADE)

The following describes the operations in group scan mode under group-A priority control (i.e. ADGSPCR.GBRSCN =

1 and ADGSPCR.GBRP = 0) when channel 0 is selected for group A and channels 1 to 3 are selected for group B.

(1) When input of a trigger for group B sets the ADCSR.ADST bit to 1 (A/D conversion start), conversion for the ANn

channels selected in the ADANSB0 and ADANSB1 registers, starting from the channel with the smallest number n.

(2) On completion of A/D conversion, the result is stored in the corresponding A/D data register (ADDRy).

(3) The ADCSR.ADST bit is cleared on the input of a trigger for group A while operation for A/D conversion in group

B is in progress, and the latter is discontinued. After that, the ADCSR.ADST bit is set to 1 (A/D conversion start),

and conversion for the ANn channels selected in the ADANSA0 and ADANSA1 registers, starting from the channel

with the smallest number n.

(4) On completion of A/D conversion on a single channel, the result is stored in the corresponding A/D data register

(ADDRy).

(5) An S12ADI0 interrupt request is generated if the setting of the ADCSR.ADIE bit is 1 (S12ADI0 interrupt upon

scanning completion enabled).

(6) After the ADST bit is automatically cleared, again, the bit is automatically set to 1 (A/D conversion start) and

conversion for the ANn channels of group B selected in the ADANSB0 and ADANSB1 registers, starting from the

channel with the smallest number n.

(7) On completion of A/D conversion on a single channel, the result is stored in the corresponding A/D data register

(ADDRy).

(8) A GBADI interrupt request is generated if the setting of the ADCSR.GBADIE bit is 1 (GBADI interrupt upon

group B scanning completion enabled).

(9) The ADST bit remains 1 (A/D conversion start) during A/D conversion and is automatically cleared on completion

of conversion, after which the A/D converter enters a wait state.

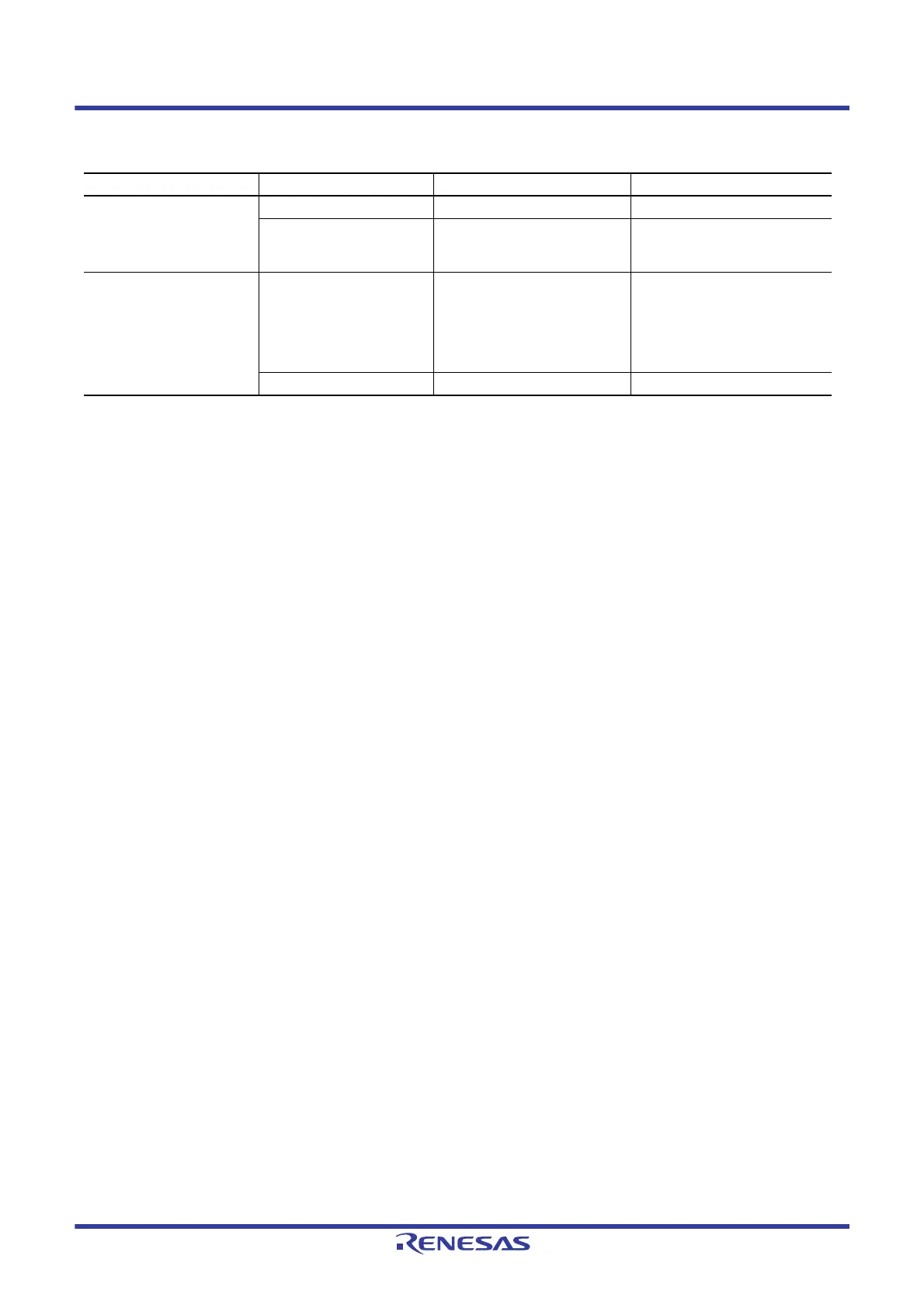

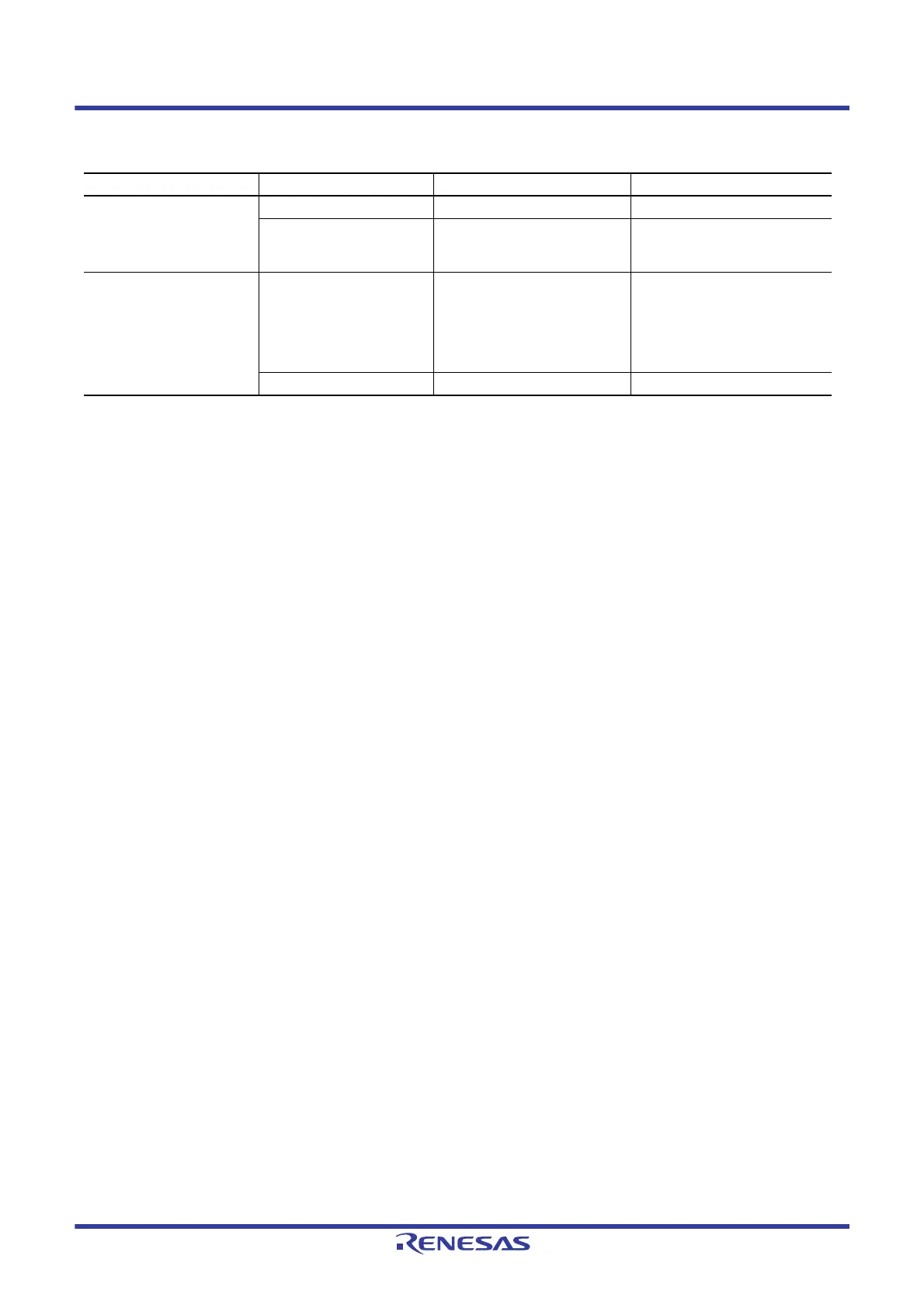

Table 44.9 Control of A/D Conversion Operations According to the Settings of the ADGSPCR.GBRSCN Bit

A/D Conversion Operation Trigger Input ADGSPCR.GBRSCN = 0 ADGSPCR.GBRSCN = 1

When A/D conversion for

group A is in progress

Input of trigger for group A Trigger input is ineffective. Trigger input is ineffective.

Input of trigger for group B Trigger input is ineffective. A/D conversion is performed on

group B after A/D conversion on

group A is completed.

When A/D conversion for

group B is in progress

Input of trigger for group A Conversion for group B that is in

progress is discontinued and

conversion for group A starts.

Conversion in progress for

group B is discontinued and

conversion for group A starts.

Conversion for group B starts

after conversion for group A is

completed.

Input of trigger for group B Trigger input is ineffective. Trigger input is ineffective.

Loading...

Loading...