R01UH0823EJ0100 Rev.1.00 Page 1627 of 1823

Jul 31, 2019

RX23W Group 45. 12-Bit D/A Converter (R12DAA)

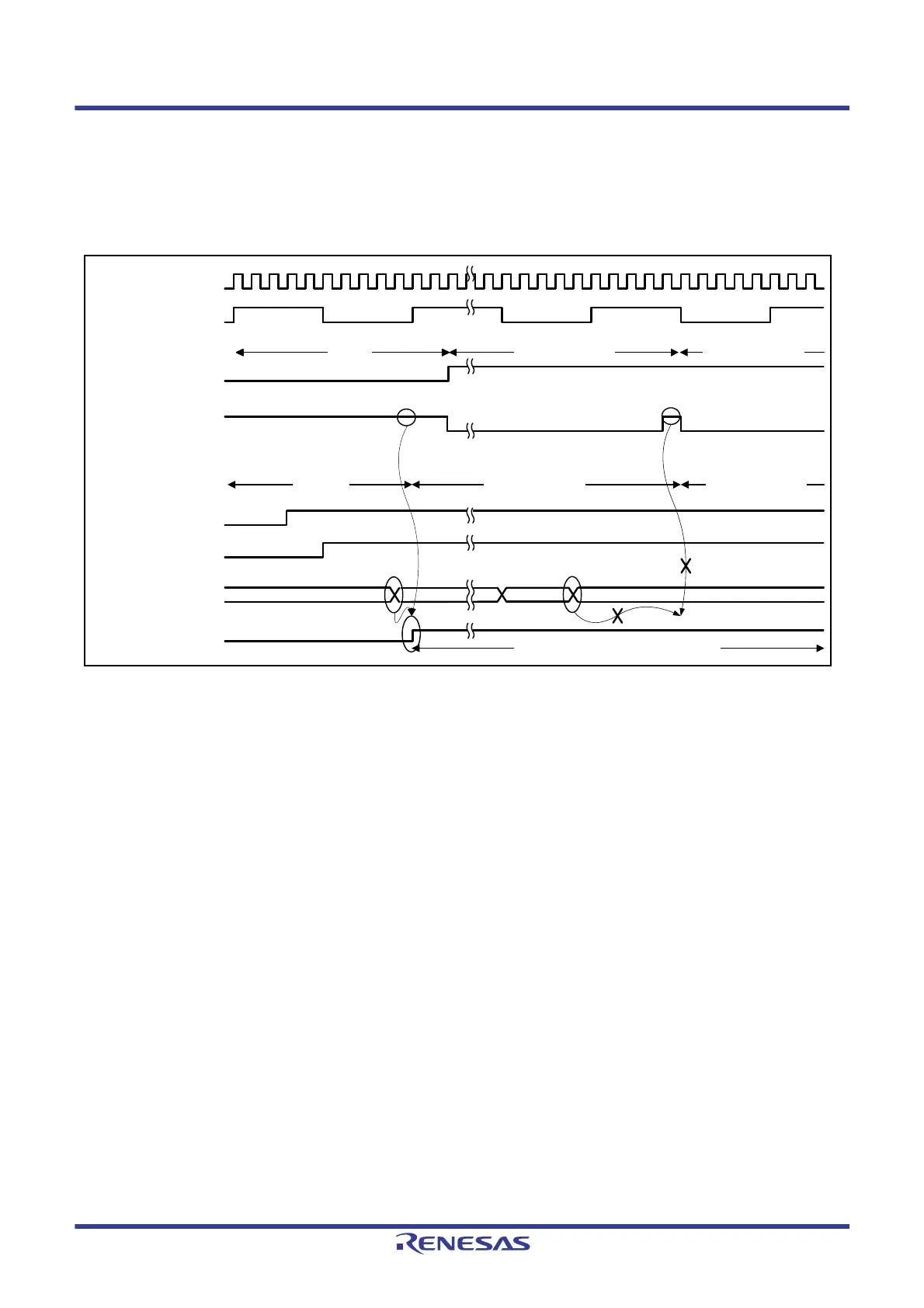

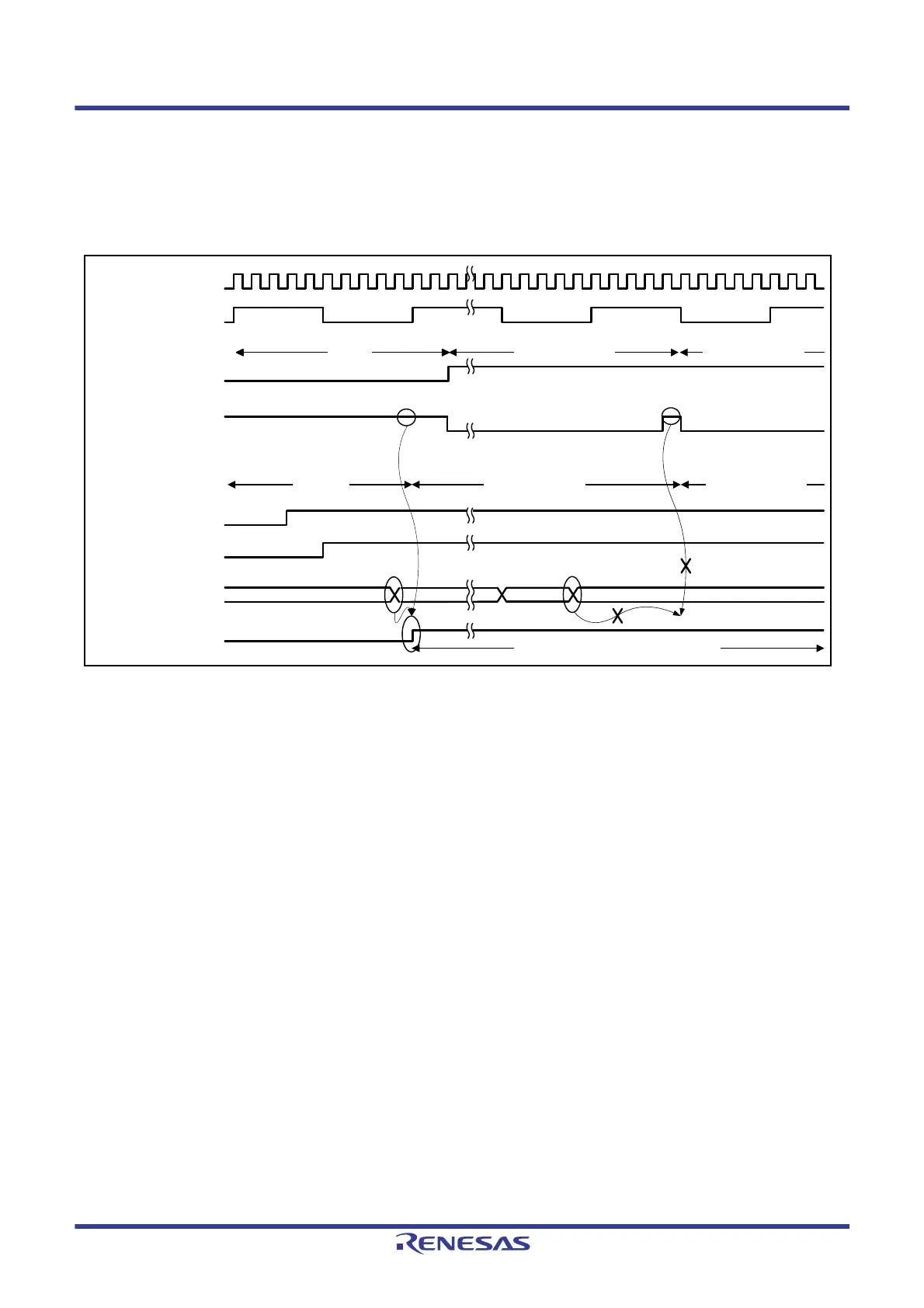

When ADCLK is faster than PCLKB, the 12-bit D/A converter may not be able to capture a 12-bit A/D converter

synchronous D/A conversion enable signal for one ADCLK cycle which is output between A/D conversion 1 and A/D

conversion 2.

Figure 45.4 shows example when the 12-bit D/A converter cannot capture the 12-bit A/D converter

synchronous D/A conversion enable signal. In this case, the DA0 output is held at the level of the post-D/A conversion

value A.

Figure 45.4 Example When the 12-Bit D/A Converter Cannot Capture the 12-Bit A/D Converter Synchronous

D/A Conversion Enable Signal

DAADSCR.DAADST bit

DADR0 register

DA0 output

A

C

PCLKB

12-bit A/D converter

synchronous D/A

conversion enable

signal (internal signal)

DACR.DAOE0 bit

ADST bit

B

(1)

(2)

(3)

(3) (3)

A/D conversion 2A/D conversion 1Halted

Standby D/A conversion A D/A conversion C

Post-D/A conversion value A output

ADCLK

Disabled

Disabled

12-bit A/D conversion

12-bit D/A conversion

Loading...

Loading...