R01UH0823EJ0100 Rev.1.00 Page 390 of 1823

Jul 31, 2019

RX23W Group 19. Data Transfer Controller (DTCa)

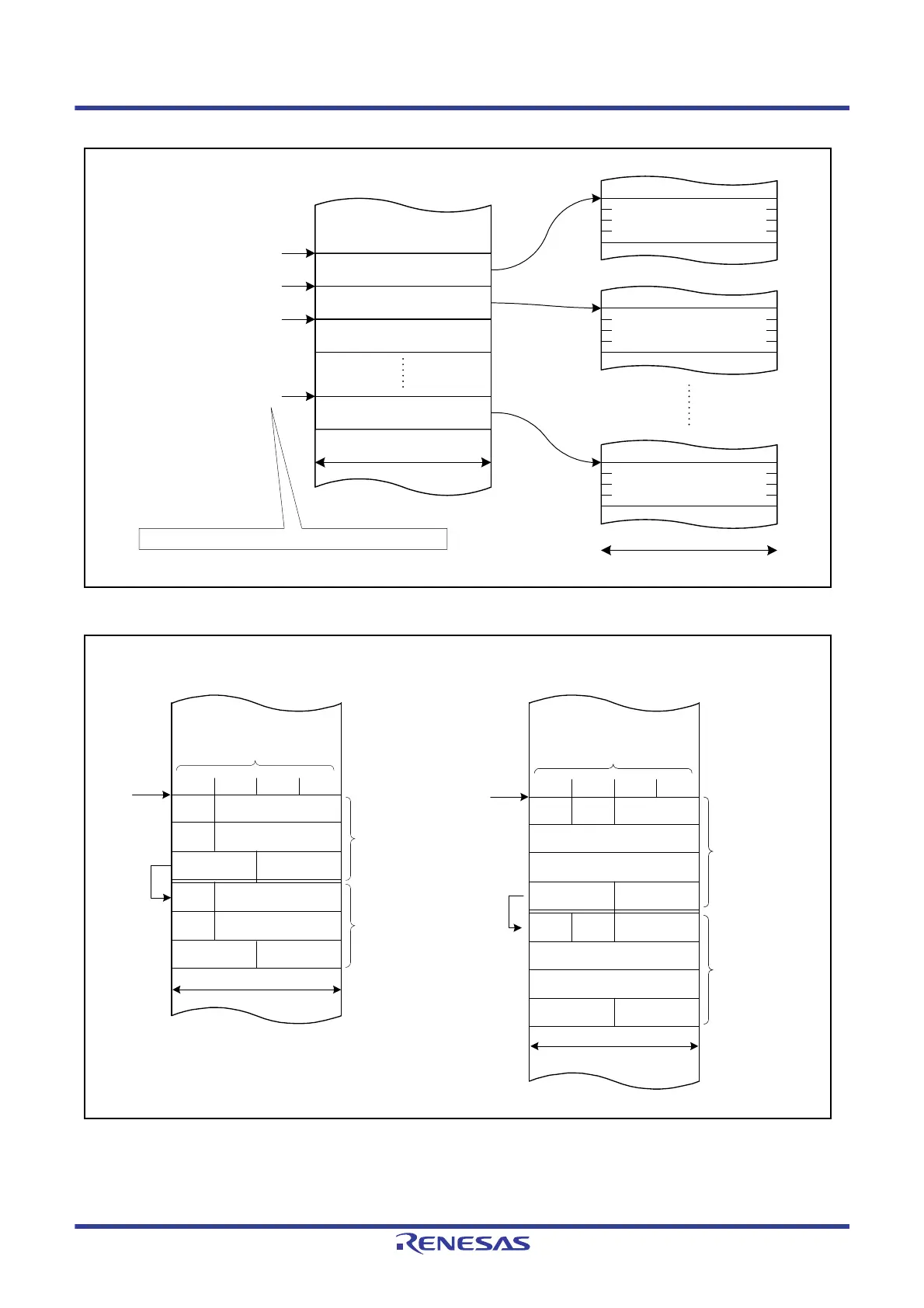

Figure 19.2 DTC Vector Table and Transfer Information

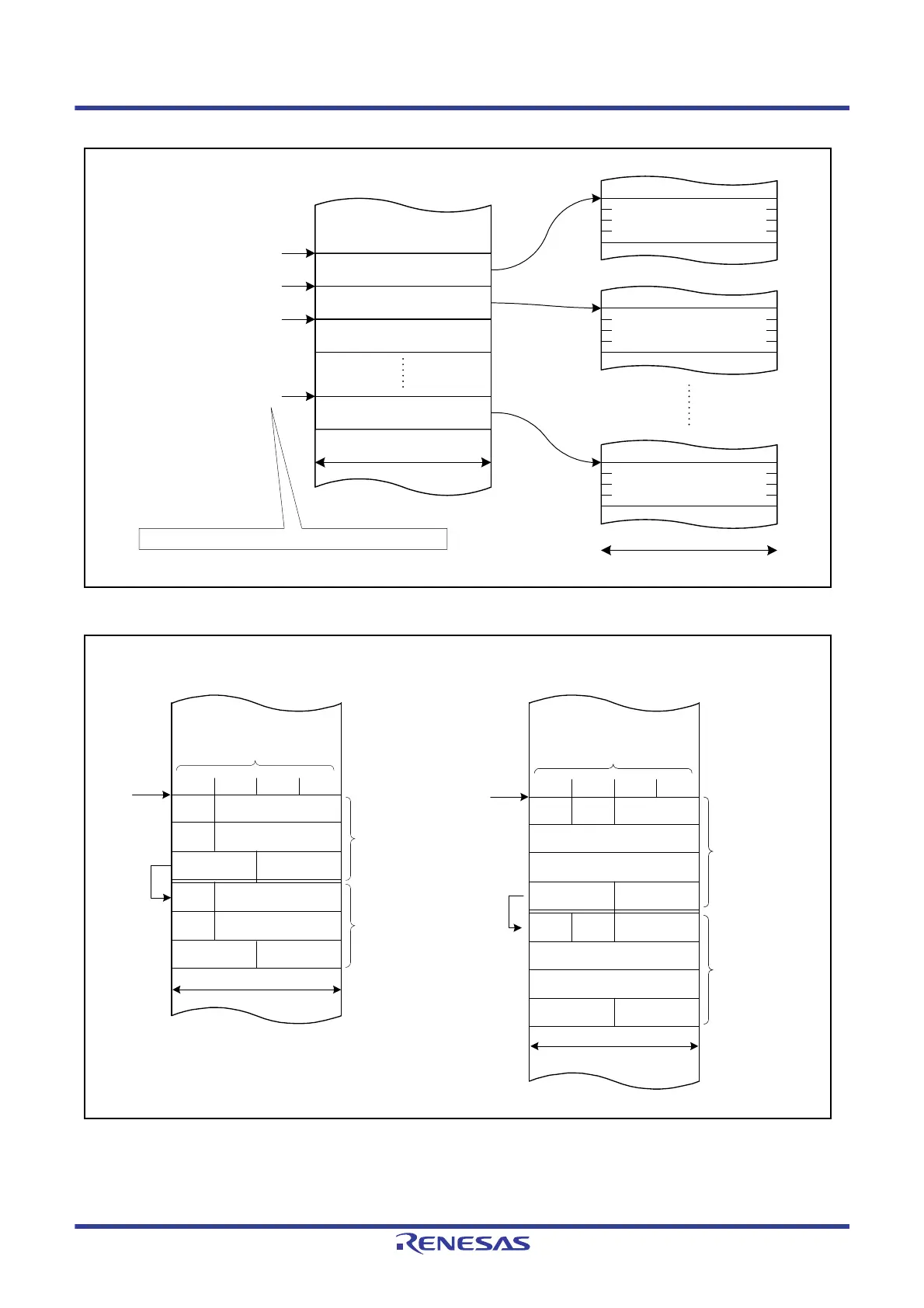

Figure 19.3 Allocation of Transfer Information in the RAM Area

DTC vector table

Start address of

transfer information 0

Start address of

transfer information 1

Start address of

transfer information n

4 bytes

+4n

+4

DTC vector base address

Start address of

transfer information 2

+8

Vector address = DTCVBR + vector number × 4

Transfer information 0

Transfer information 1

Transfer information n

4 bytes

Transfer information

per transfer

(16 bytes)

Transfer information

for the second

transfer in chain

transfer mode

(16 bytes)

Transfer information

for the second

transfer in chain

transfer mode

(12 bytes)

Start address

1 (2)

0 (3)

MRA SAR

MRB DAR

CRA

CRB

MRA SAR

MRB

DAR

CRA CRB

MRA MRB

Reserved

(0000h)

MRA MRB

SAR

DAR

CRA CRB

CRA CRB

SAR

DAR

3 (0) 2 (1)

Allocation of transfer information in

short-address mode

Transfer information

per transfer

(12 bytes)

Allocation of transfer information in

full-address mode

Start address

4 bytes

Reserved

(0000h)

4 bytes

( ): Lower address to be allocated

in the big-endian area

1 (2) 0 (3)3 (0) 2 (1)

Lower address

Chain

transfer

Chain

transfer

( ): Lower address to be allocated

in the big-endian area

Lower address

Loading...

Loading...