R01UH0823EJ0100 Rev.1.00 Page 1303 of 1823

Jul 31, 2019

RX23W Group 37. Serial Sound Interface (SSI)

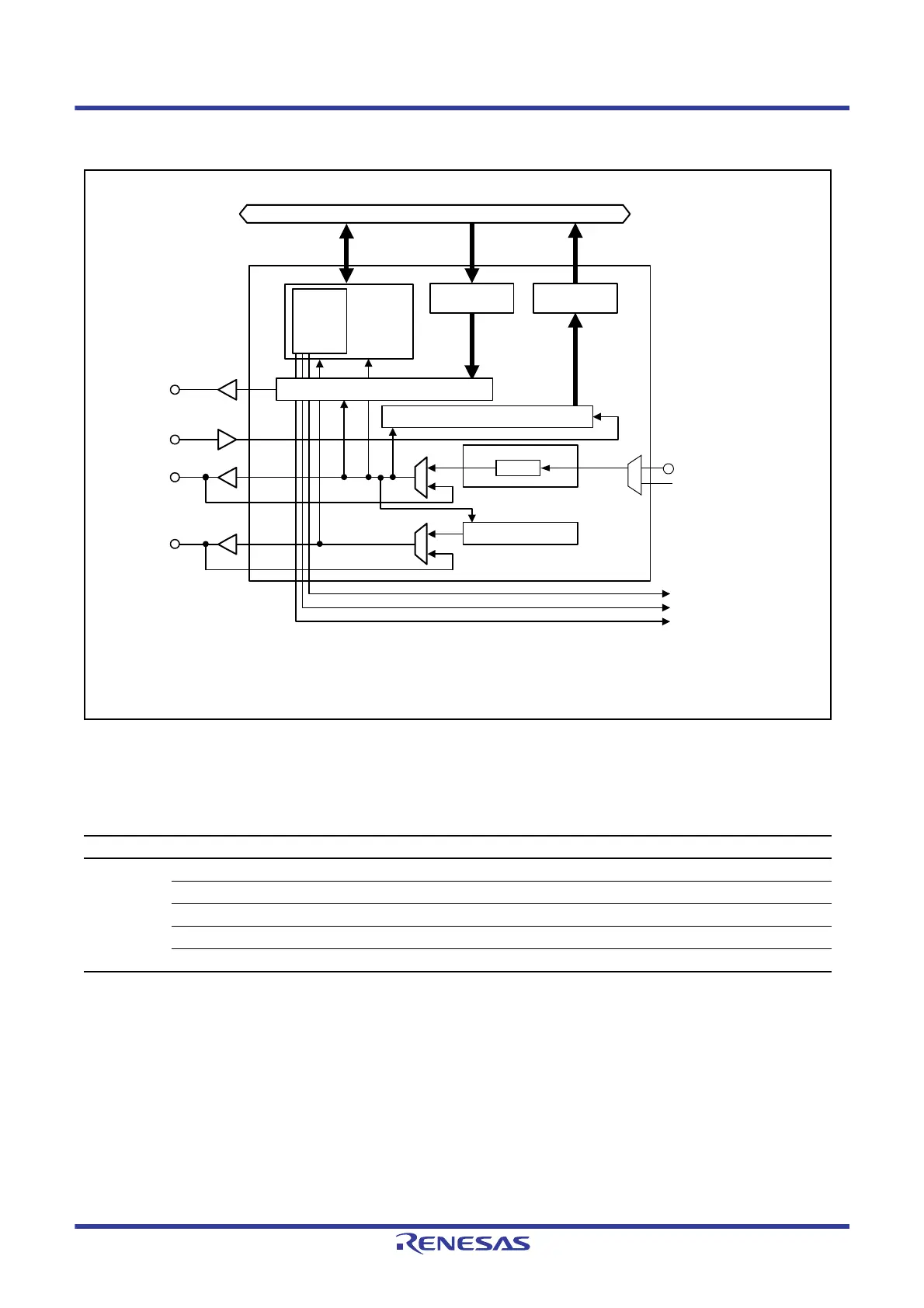

Figure 37.1 shows a block diagram of SSI (SSI0).

Figure 37.1 Block Diagram of SSI (SSI0)

Table 37.2 lists the I/O pins of the SSI.

Table 37.2 SSI I/O Pins

Channel Pin Name I/O Description

SSI0 SSISCK0 I/O Serial bit clock pin

SSIWS0 I/O Word selection pin

SSITXD0 Output Serial data output pin

SSIRXD0 Input Serial data input pin

AUDIO_MCLK Input Master clock for audio pin (input master clock)

Bit clock control

SSISCK0

SSIWS0

Control

circuit

MSB Receive shift register LSB

Bit counter

Divider

Registers

SSICR

SSISR

SSIFCR

SSIFSR

SSITDMR

MSB Transmit shift register LSB

SSITXD0

SSICR: Control register

SSISR: Status register

SSITDMR: TDM mode register

SSIFCR: FIFO control register

SSIFSR: FIFO status register

SSIFTDR: Transmit FIFO data register

SSIFRDR: Receive FIFO data register

MCLK: Master clock

SSIFTDR

(8-stage FIFO)

SSIFRDR

(8-stage FIFO)

Internal peripheral bus

SSIF0 interrupt request

SSIRXI0 interrupt request

SSITXI0 interrupt request

SSIRXD0

Loading...

Loading...