R01UH0823EJ0100 Rev.1.00 Page 414 of 1823

Jul 31, 2019

RX23W Group 20. Event Link Controller (ELC)

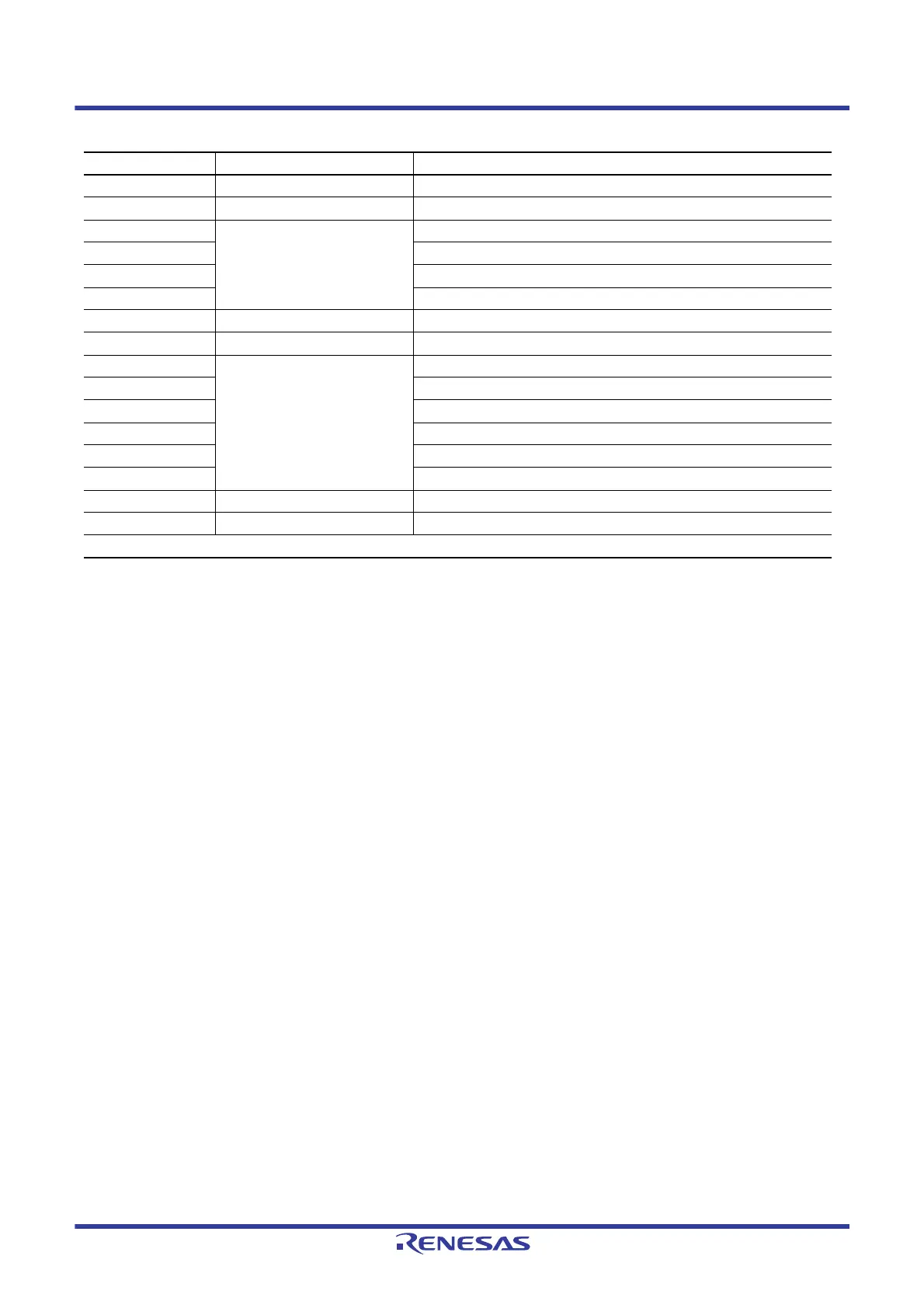

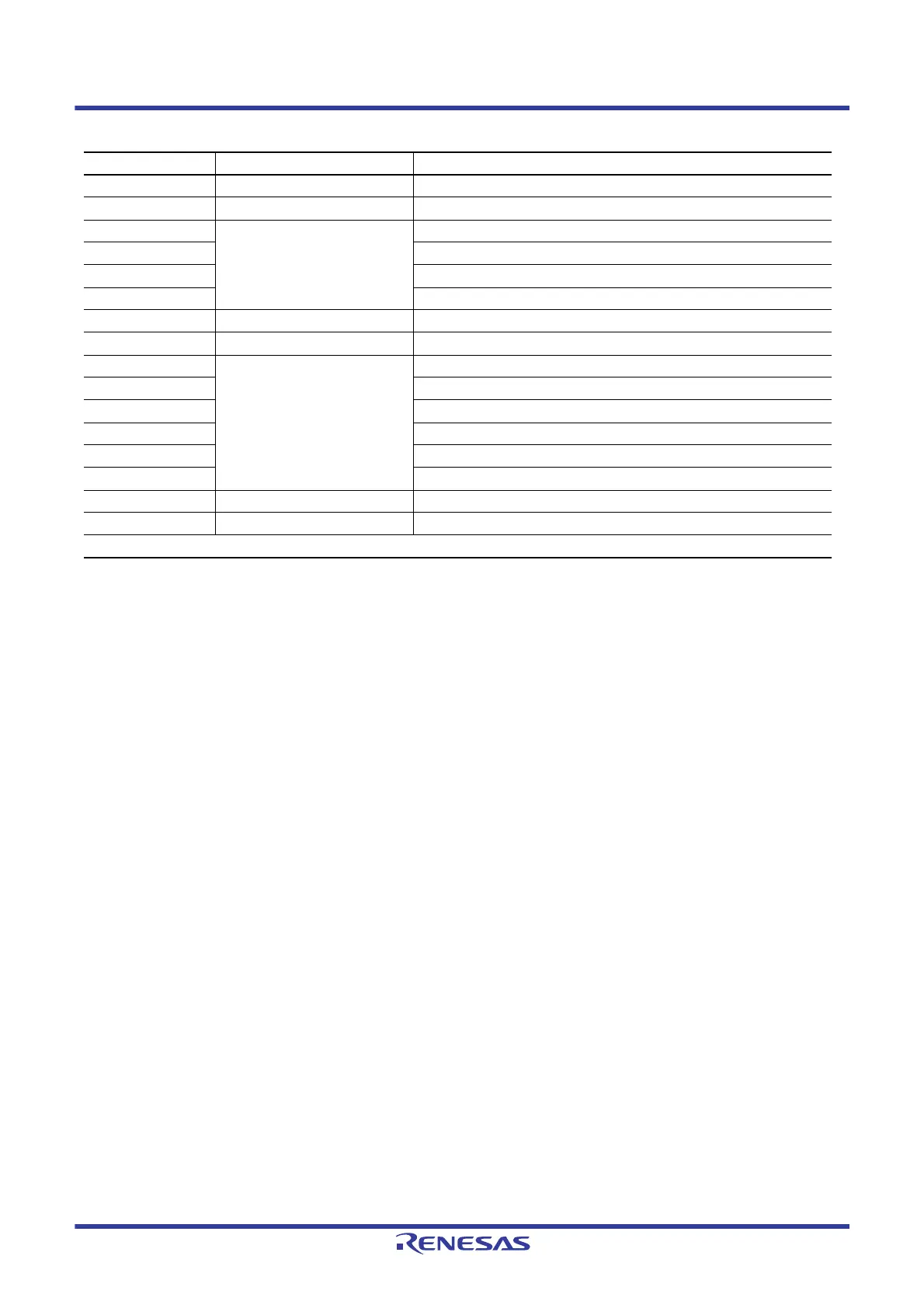

58h 12-bit A/D converter S12AD A/D conversion end

5Bh Voltage detection circuit LVD1 voltage detection

5Dh DMA controller DMAC0 transfer end

5Eh DMAC1 transfer end

5Fh DMAC2 transfer end

60h DMAC3 transfer end

61h Data transfer controller DTC transfer end

62h Clock generation circuit Oscillation stop detection of clock generation circuit

63h I/O ports Input edge detection of input port group 1

64h Input edge detection of input port group 2

65h Input edge detection of single input port 0

66h Input edge detection of single input port 1

67h Input edge detection of single input port 2

68h Input edge detection of single input port 3

69h Event link controller Software event

6Ah Data operation circuit DOC data operation condition met

Settings other than above are prohibited.

Table 20.3

Correspondence between Values Set in ELSRn.ELS[7:0] Bits and Event Signals (2/2)

ELS[7:0] Bit Value Peripheral Modules Event Signal Set in ELSRn

Loading...

Loading...