R01UH0823EJ0100 Rev.1.00 Page 478 of 1823

Jul 31, 2019

RX23W Group 23. Multi-Function Timer Pulse Unit 2 (MTU2a)

Note: This setting is ignored when MTU1 is in phase counting mode.

Note: This setting is ignored when MTU2 is in phase counting mode.

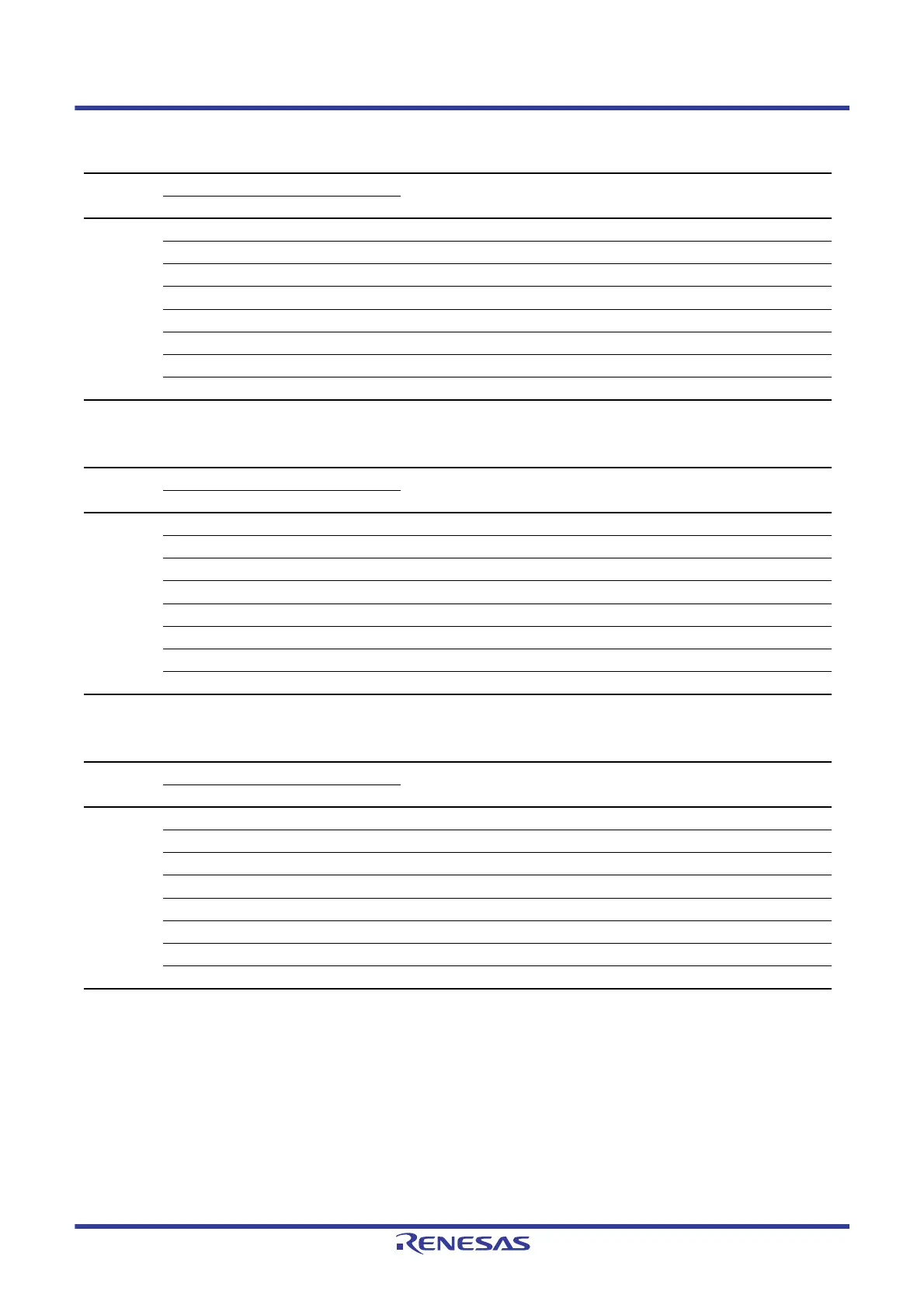

Table 23.7 TPSC[2:0] (MTU1)

Channel

Bit 2 Bit 1 Bit 0

DescriptionTPSC[2] TPSC[1] TPSC[0]

MTU1 0 0 0 Internal clock: counts on PCLK/1

0 0 1 Internal clock: counts on PCLK/4

0 1 0 Internal clock: counts on PCLK/16

0 1 1 Internal clock: counts on PCLK/64

1 0 0 External clock: counts on MTCLKA pin input

1 0 1 External clock: counts on MTCLKB pin input

1 1 0 Internal clock: counts on PCLK/256

1 1 1 Counts on MTU2.TCNT overflow/underflow

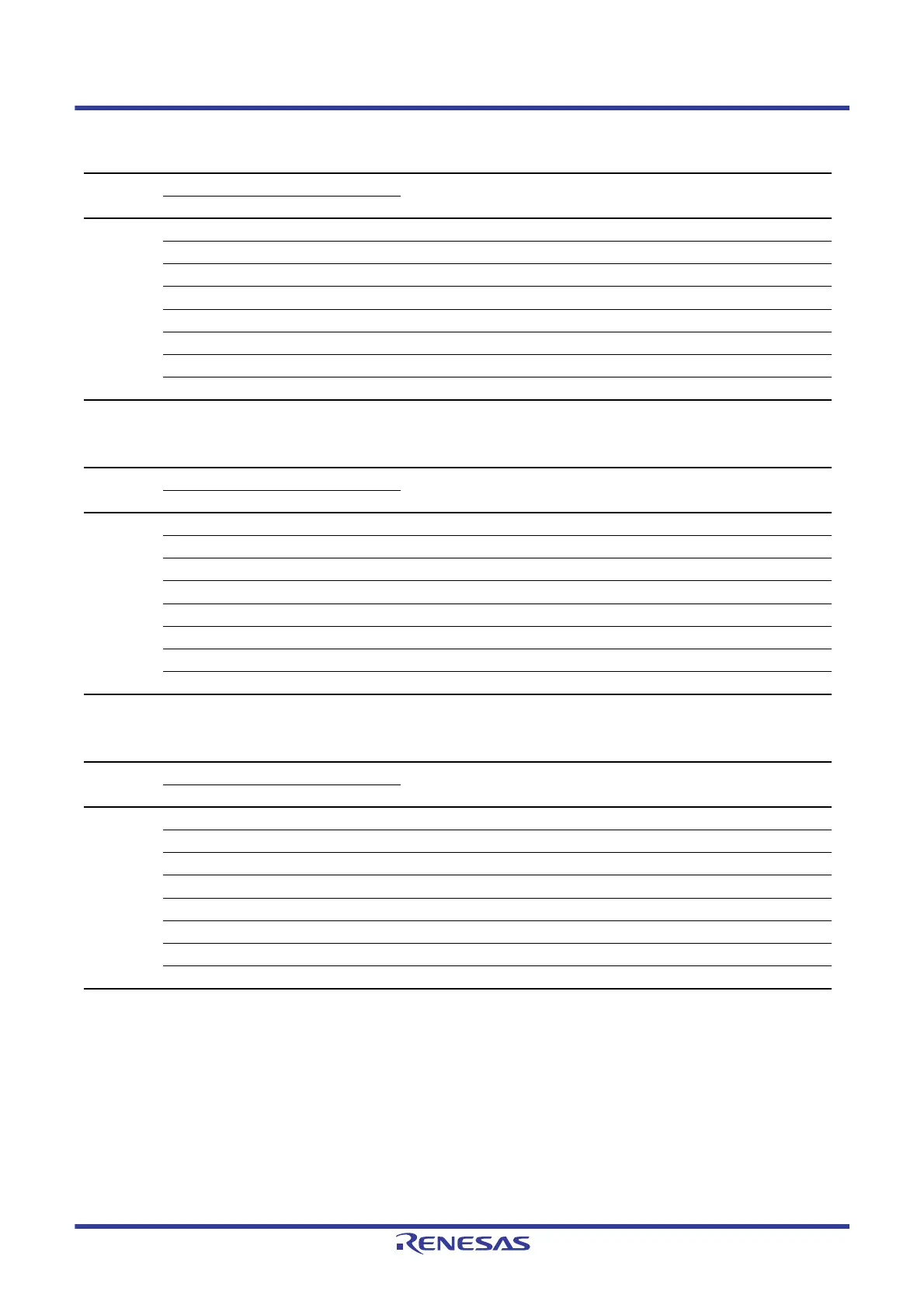

Table 23.8 TPSC[2:0] (MTU2)

Channel

Bit 2 Bit 1 Bit 0

DescriptionTPSC[2] TPSC[1] TPSC[0]

MTU2 0 0 0 Internal clock: counts on PCLK/1

0 0 1 Internal clock: counts on PCLK/4

0 1 0 Internal clock: counts on PCLK/16

0 1 1 Internal clock: counts on PCLK/64

1 0 0 External clock: counts on MTCLKA pin input

1 0 1 External clock: counts on MTCLKB pin input

1 1 0 External clock: counts on MTCLKC pin input

1 1 1 Internal clock: counts on PCLK/1024

Table 23.9 TPSC[2:0] (MTU3 and MTU4)

Channel

Bit 2 Bit 1 Bit 0

DescriptionTPSC[2] TPSC[1] TPSC[0]

MTU3,

MTU4

0 0 0 Internal clock: counts on PCLK/1

0 0 1 Internal clock: counts on PCLK/4

0 1 0 Internal clock: counts on PCLK/16

0 1 1 Internal clock: counts on PCLK/64

1 0 0 Internal clock: counts on PCLK/256

1 0 1 Internal clock: counts on PCLK/1024

1 1 0 External clock: counts on MTCLKA pin input

1 1 1 External clock: counts on MTCLKB pin input

Loading...

Loading...