R01UH0823EJ0100 Rev.1.00 Page 477 of 1823

Jul 31, 2019

RX23W Group 23. Multi-Function Timer Pulse Unit 2 (MTU2a)

Note 1. Synchronous operation is selected by setting the TSYR.SYNCn bit (n = 0, 3, 4) to 1.

Note 2. When TGRC or TGRD is used as a buffer register, TCNT is not cleared because the buffer register setting has priority and

compare match/input capture does not occur.

Note 1. Synchronous operation is selected by setting the TSYR.SYNCn bit (n = 1, 2) to 1.

Note 2. Bit 7 is reserved in MTU1 and MTU2. This bit is read as 0. The write value should be 0.

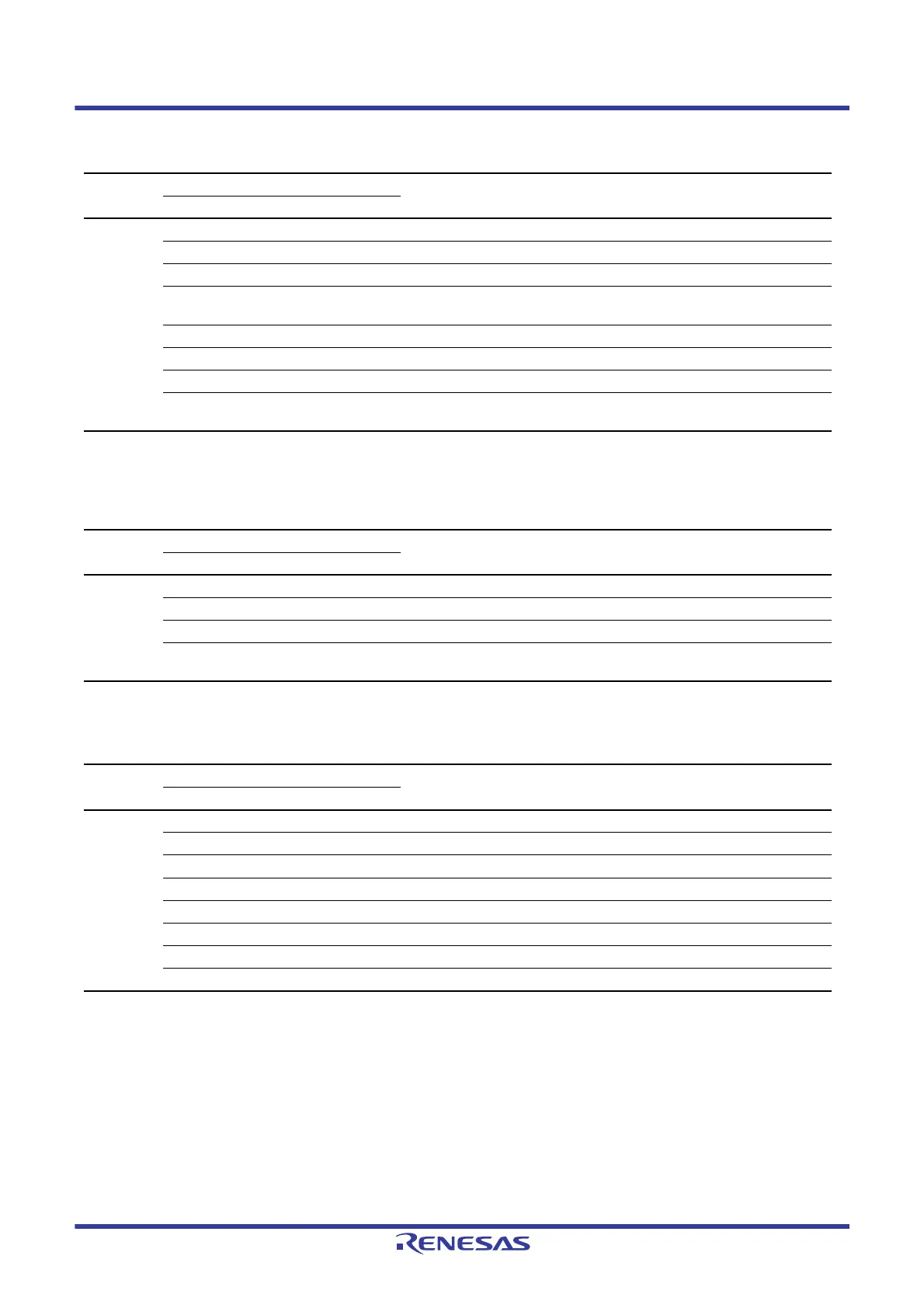

Table 23.4 CCLR[2:0] (MTU0, MTU3, and MTU4)

Channel

Bit 7 Bit 6 Bit 5

DescriptionCCLR[2] CCLR[1] CCLR[0]

MTU0,

MTU3,

MTU4

0 0 0 TCNT clearing disabled

0 0 1 TCNT cleared by TGRA compare match/input capture

0 1 0 TCNT cleared by TGRB compare match/input capture

0 1 1 TCNT cleared by counter clearing in another channel performing

synchronous clearing/synchronous operation*

1

1 0 0 TCNT clearing disabled

1 0 1 TCNT cleared by TGRC compare match/input capture*

2

1 1 0 TCNT cleared by TGRD compare match/input capture*

2

1 1 1 TCNT cleared by counter clearing in another channel performing

synchronous clearing/synchronous operation*

1

Table 23.5 CCLR[2:0] (MTU1 and MTU2)

Channel

Bit 7 Bit 6 Bit 5

DescriptionReserved*

2

CCLR[1] CCLR[0]

MTU1,

MTU2

0 0 0 TCNT clearing disabled

0 0 1 TCNT cleared by TGRA compare match/input capture

0 1 0 TCNT cleared by TGRB compare match/input capture

0 1 1 TCNT cleared by counter clearing in another channel performing

synchronous clearing/synchronous operation*

1

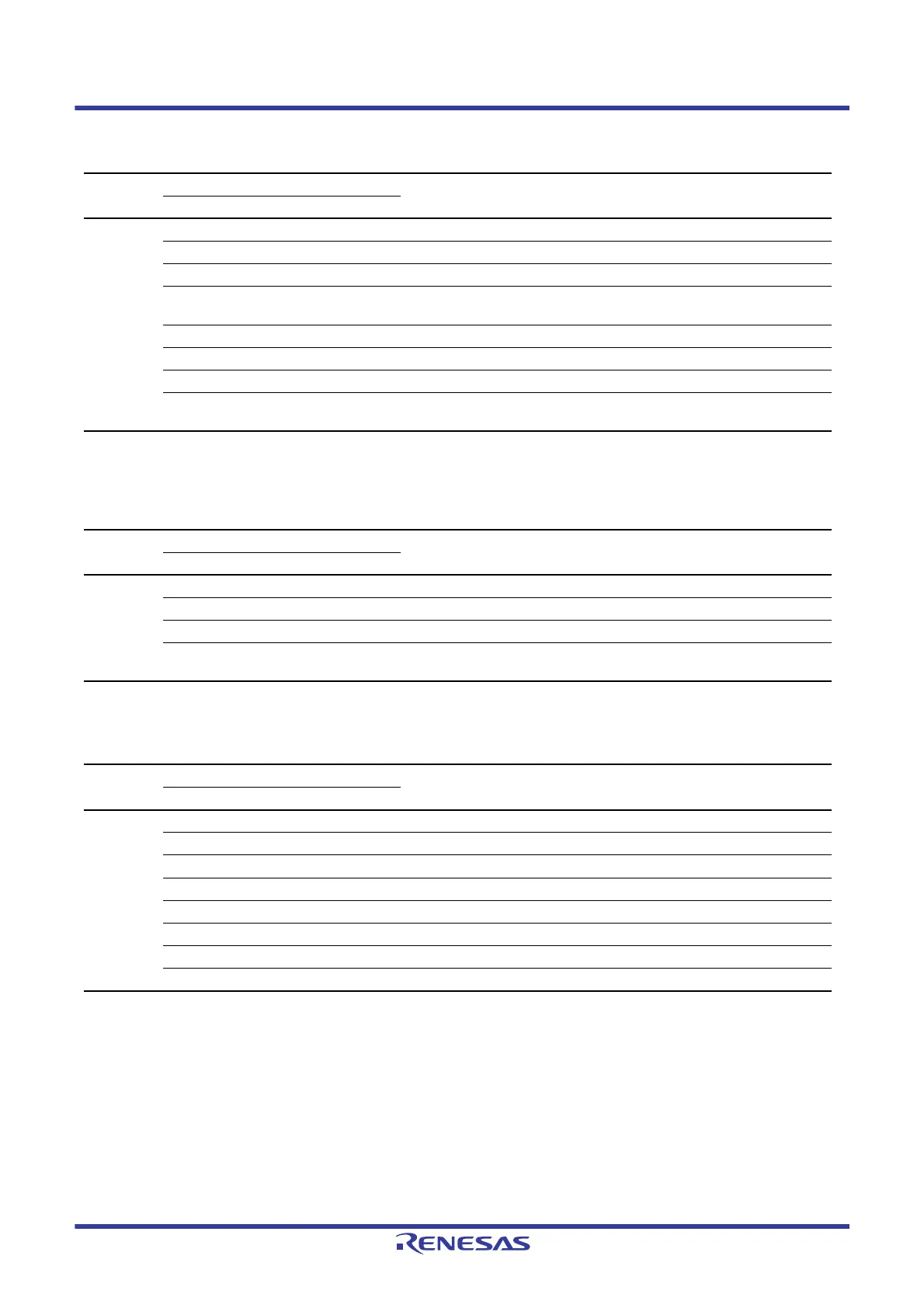

Table 23.6 TPSC[2:0] (MTU0)

Channel

Bit 2 Bit 1 Bit 0

DescriptionTPSC[2] TPSC[1] TPSC[0]

MTU0 0 0 0 Internal clock: counts on PCLK/1

0 0 1 Internal clock: counts on PCLK/4

0 1 0 Internal clock: counts on PCLK/16

0 1 1 Internal clock: counts on PCLK/64

1 0 0 External clock: counts on MTCLKA pin input

1 0 1 External clock: counts on MTCLKB pin input

1 1 0 External clock: counts on MTCLKC pin input

1 1 1 External clock: counts on MTCLKD pin input

Loading...

Loading...