R01UH0823EJ0100 Rev.1.00 Page 482 of 1823

Jul 31, 2019

RX23W Group 23. Multi-Function Timer Pulse Unit 2 (MTU2a)

The MTU has a total of seven TIOR registers, one for MTU0, MTU1, and MTU2, two each for MTU3, and MTU4.

The TIOR register should be set when the TMDR register is set to select normal mode, PWM mode, or phase counting

mode.

The initial output specified by the TIOR register is valid when the counter is stopped (the TSTR.CSTn bit is set to 0).

Note also that, in PWM mode 2, the output at the point at which the counter is set to 0 is specified.

When the TGRC or TGRD register is designated for buffer operation, this setting is invalid and the register operates as a

buffer register.

x: Don't care

Note 1. When PCLK/1 is selected as the count clock for MTU1, MTU0 input capture is not generated. Do not select PCLK/1 as the count

clock for MTU1.

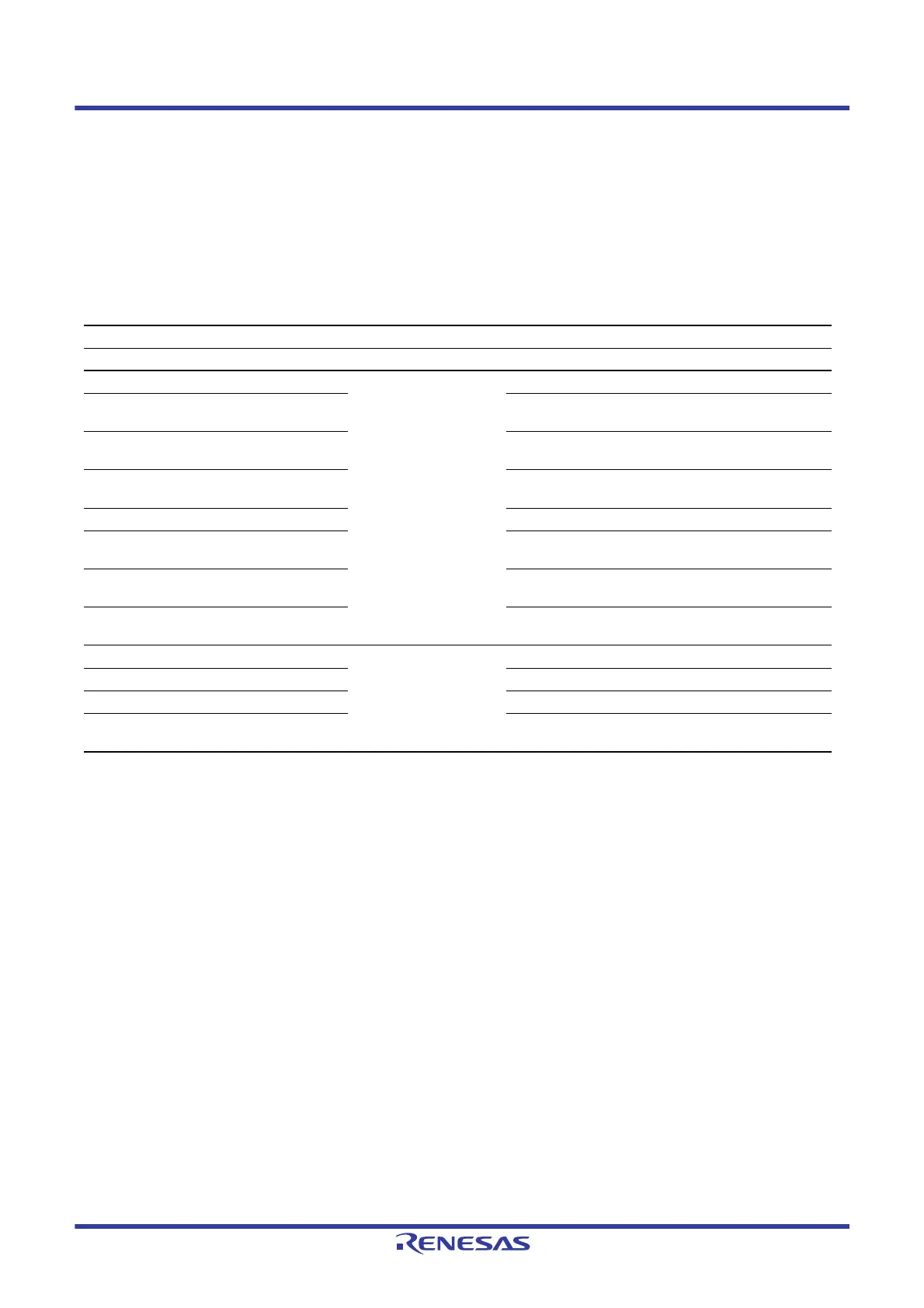

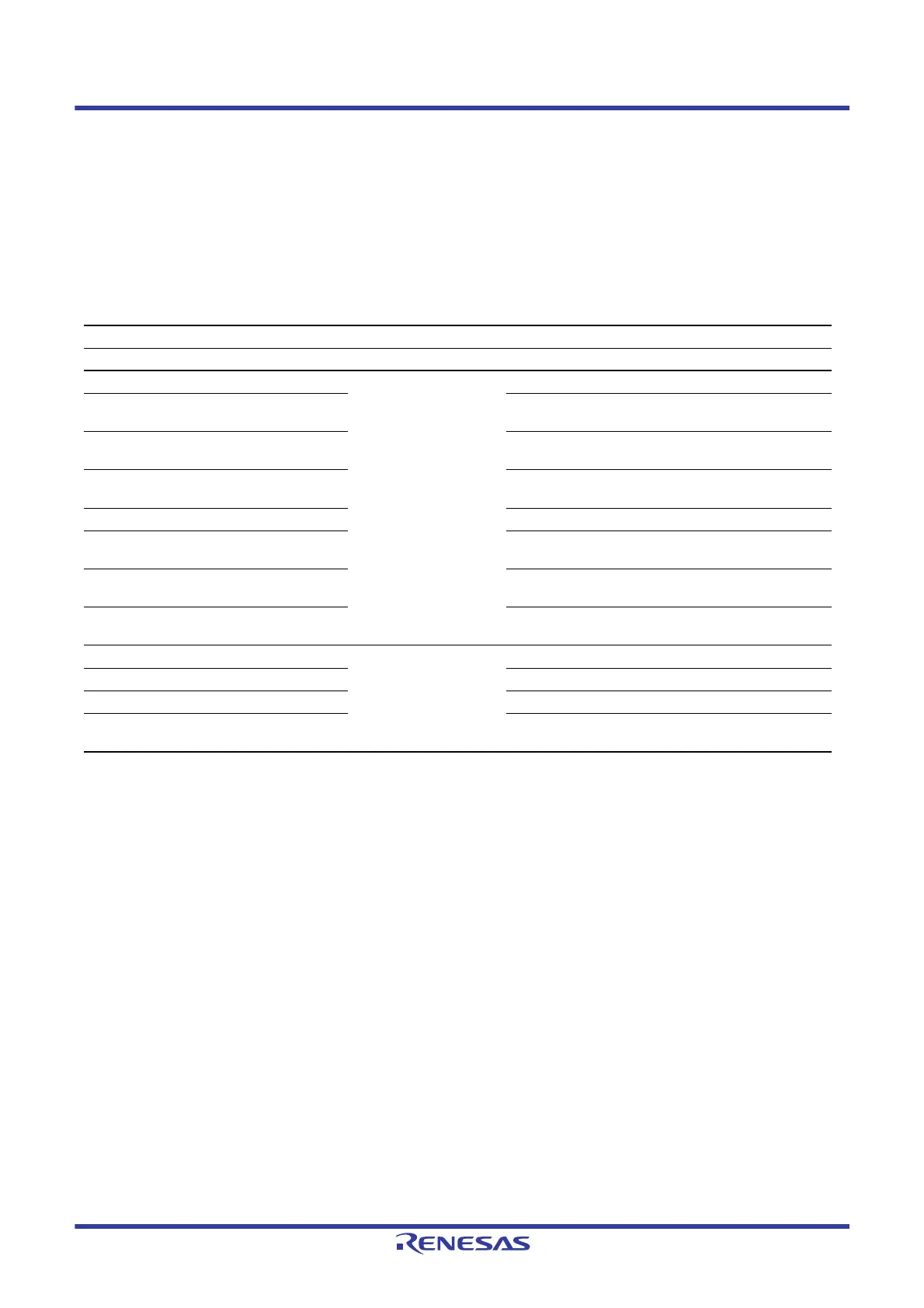

Table 23.11 TIORH (MTU0)

Bit 7 Bit 6 Bit 5 Bit 4 Description

IOB[3] IOB[2] IOB[1] IOB[0] MTU0.TGRB Function MTIOC0B Pin Function

0 0 0 0 Output compare register Output prohibited

0 0 0 1 Initial output is low.

Low output at compare match.

0 0 1 0 Initial output is low.

High output at compare match.

0 0 1 1 Initial output is low.

Toggle output at compare match.

0 1 0 0 Output prohibited

0 1 0 1 Initial output is high.

Low output at compare match.

0 1 1 0 Initial output is high.

High output at compare match.

0 1 1 1 Initial output is high.

Toggle output at compare match.

1 0 0 0 Input capture register Input capture at rising edge.

1 0 0 1 Input capture at falling edge.

1 0 1 x Input capture at both edges.

1 1 x x Capture input source is count clock in MTU1.

Input capture at MTU1.TCNT up-count/down-count.*

1

Loading...

Loading...