R01UH0823EJ0100 Rev.1.00 Page 487 of 1823

Jul 31, 2019

RX23W Group 23. Multi-Function Timer Pulse Unit 2 (MTU2a)

x: Don't care

Note 1. When the MTU0.TMDR.BFA bit is set to 1 and the MTU0.TGRC register is used as a buffer register, this setting is invalid and

input capture/output compare is not generated.

Note 2. When PCLK/1 is selected as the count clock for MTU1, MTU0 input capture is not generated. Do not select PCLK/1 as the count

clock for MTU1.

x: Don't care

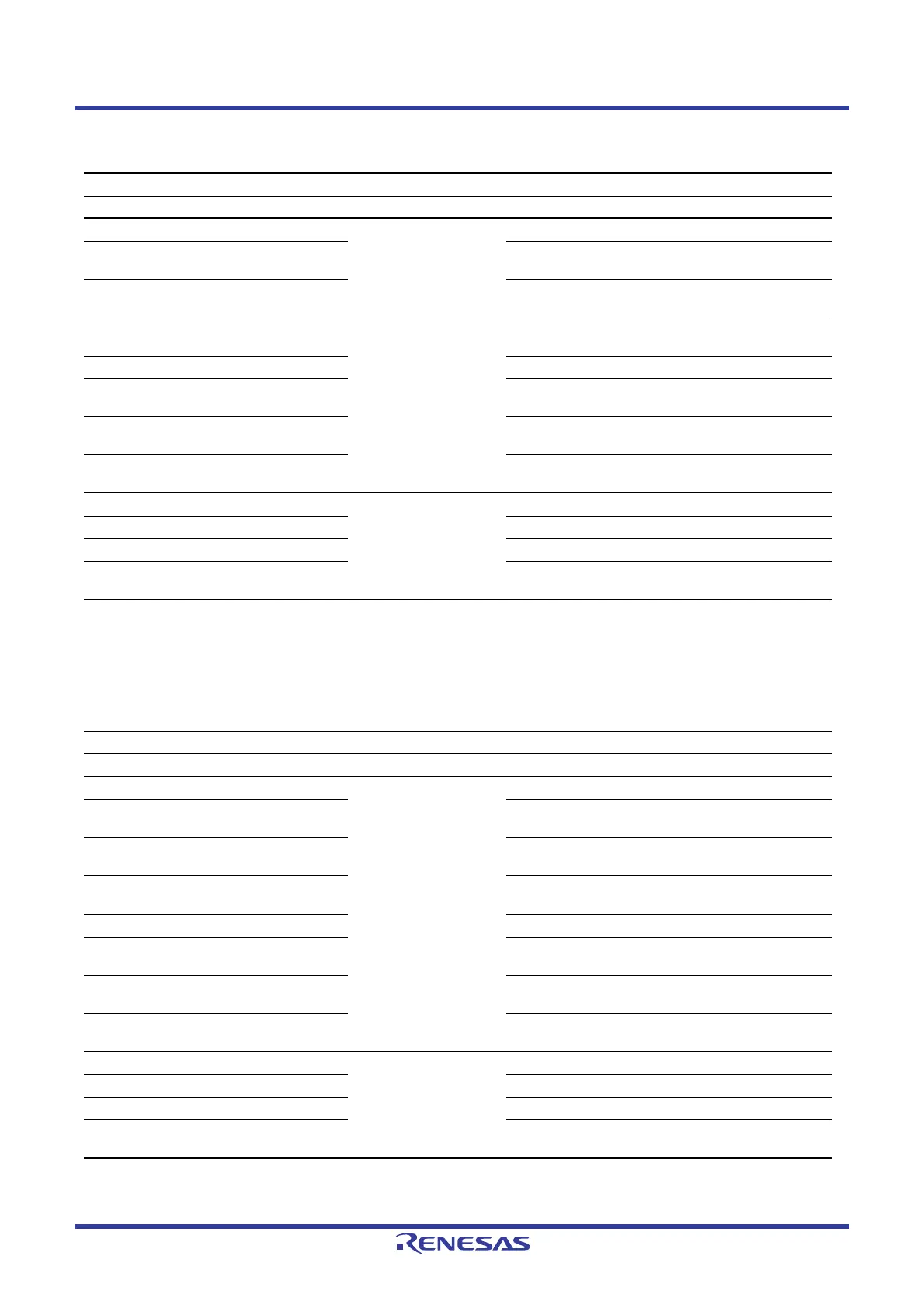

Table 23.19 TIORL (MTU0)

Bit 3 Bit 2 Bit 1 Bit 0 Description

IOC[3] IOC[2] IOC[1] IOC[0] MTU0.TGRC Function MTIOC0C Pin Function

0 0 0 0 Output compare register*

1

Output prohibited

0 0 0 1 Initial output is low.

Low output at compare match.

0 0 1 0 Initial output is low.

High output at compare match.

0 0 1 1 Initial output is low.

Toggle output at compare match.

0 1 0 0 Output prohibited

0 1 0 1 Initial output is high.

Low output at compare match.

0 1 1 0 Initial output is high.

High output at compare match.

0 1 1 1 Initial output is high.

Toggle output at compare match.

1 0 0 0 Input capture register*

1

Input capture at rising edge.

1 0 0 1 Input capture at falling edge.

1 0 1 x Input capture at both edges.

1 1 x x Capture input source is count clock in MTU1.

Input capture at MTU1.TCNT up-count/down-count.*

2

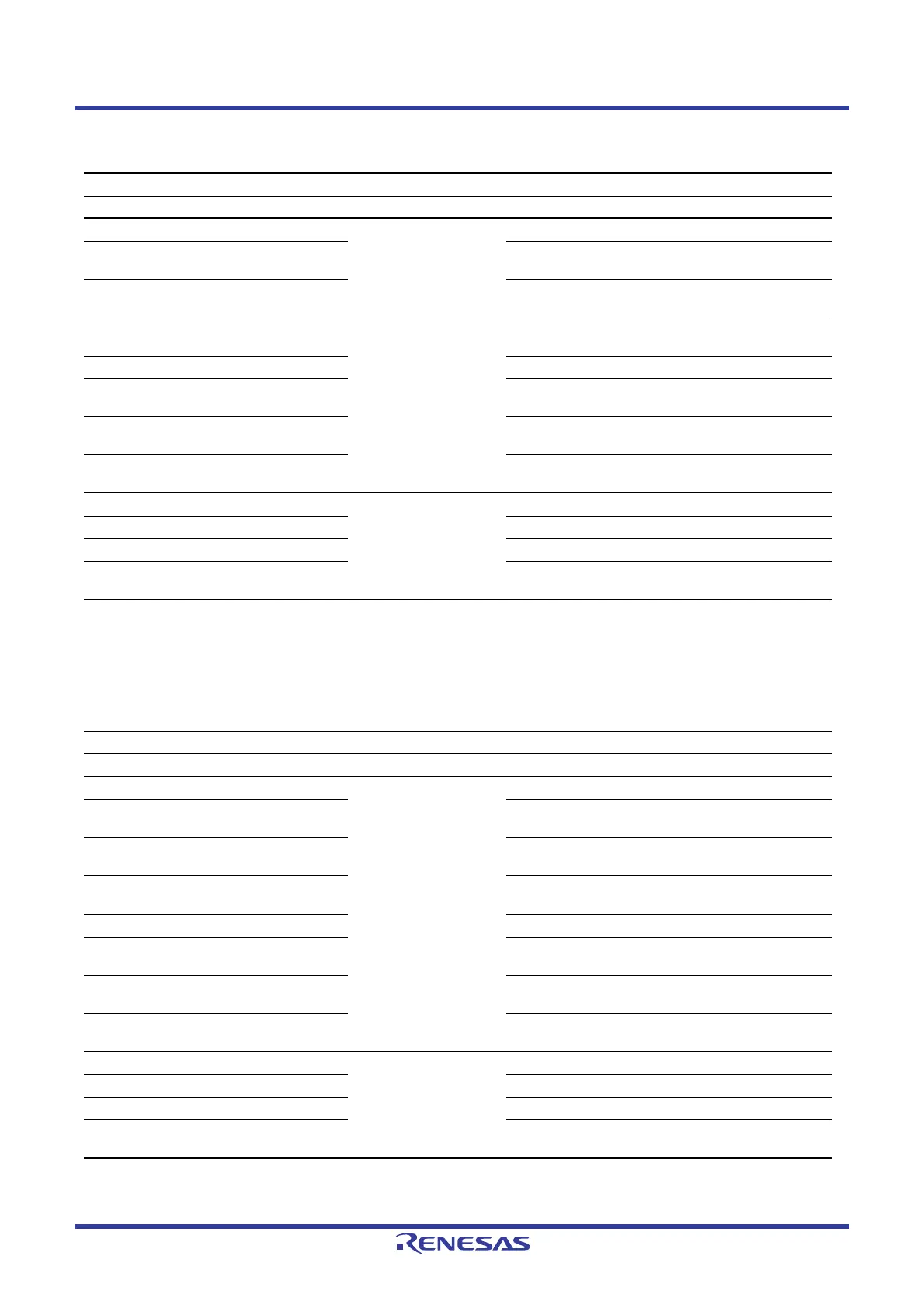

Table 23.20 TIOR (MTU1)

Bit 3 Bit 2 Bit 1 Bit 0 Description

IOA[3] IOA[2] IOA[1] IOA[0] MTU1.TGRA Function MTIOC1A Pin Function

0 0 0 0 Output compare register Output prohibited

0 0 0 1 Initial output is low.

Low output at compare match.

0 0 1 0 Initial output is low.

High output at compare match.

0 0 1 1 Initial output is low.

Toggle output at compare match.

0 1 0 0 Output prohibited

0 1 0 1 Initial output is high.

Low output at compare match.

0 1 1 0 Initial output is high.

High output at compare match.

0 1 1 1 Initial output is high.

Toggle output at compare match.

1 0 0 0 Input capture register Input capture at rising edge.

1 0 0 1 Input capture at falling edge.

1 0 1 x Input capture at both edges.

1 1 x x Input capture at generation of MTU0.TGRA compare

match/input capture.

Loading...

Loading...