R01UH0823EJ0100 Rev.1.00 Page 614 of 1823

Jul 31, 2019

RX23W Group 23. Multi-Function Timer Pulse Unit 2 (MTU2a)

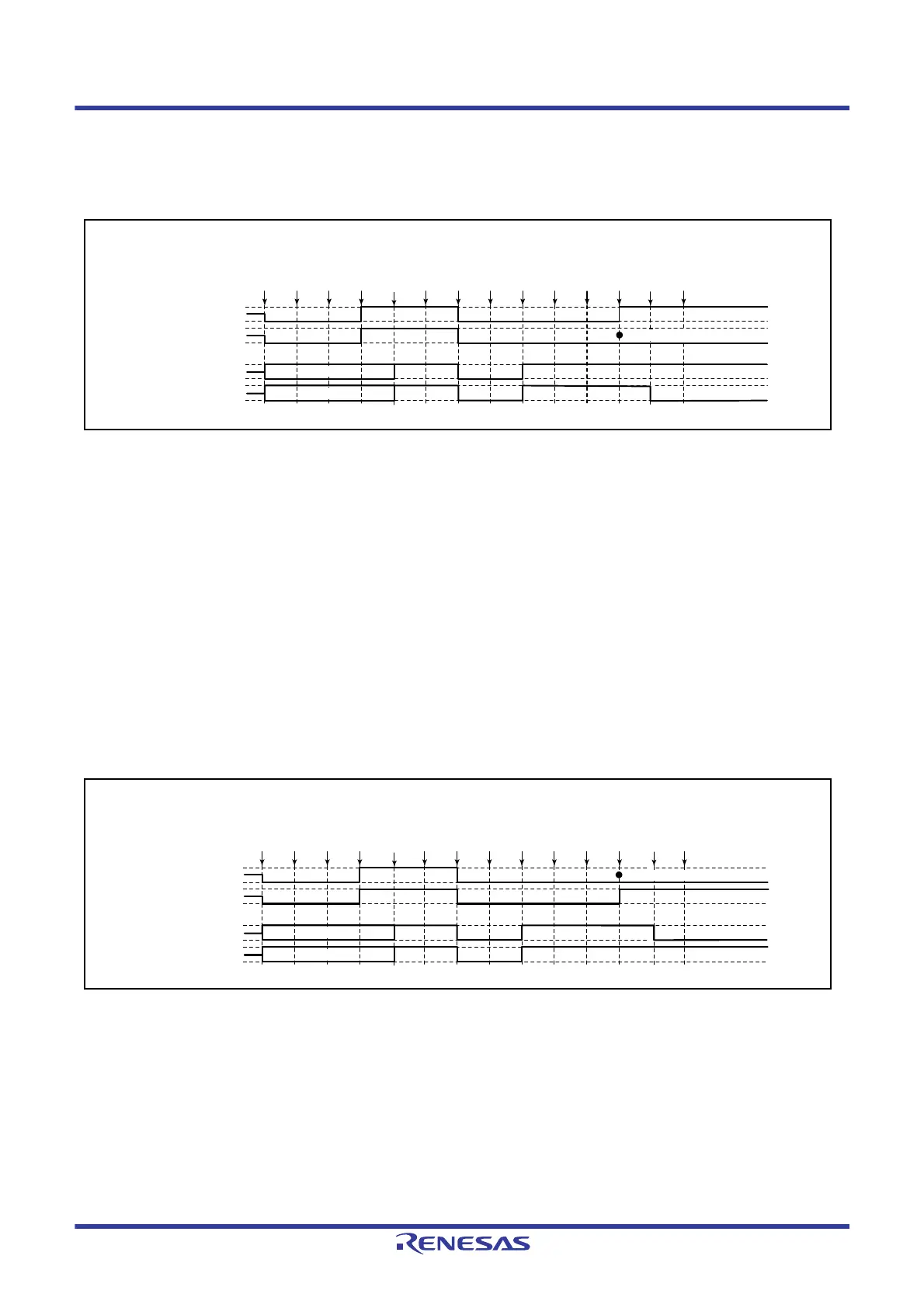

(2) Operation When Error Occurs in Normal Mode and Operation is Restarted in PWM Mode 1

Figure 23.117 shows a case in which an error occurs in normal mode and operation is restarted in PWM mode 1 after re-

setting.

Figure 23.117 Error Occurrence in Normal Mode, Recovery in PWM Mode 1

(1) to (10) are the same as in Figure 23.116.

(11)Set PWM mode 1.

(12)Set the TIOR register to initialize pins, i.e. so that the MTIOCnB (or MTIOCnD) does not produce a waveform in

PWM mode 1. If a particular level should be output, set the port direction register (PDR) and the port output data

register (PODR) so that the pins of the I/O port operate as general outputs.

(13) Use the MPC and the port mode register (PMR) for the I/O port to set up MTU output.

(14) Restart operation by setting the TSTR register.

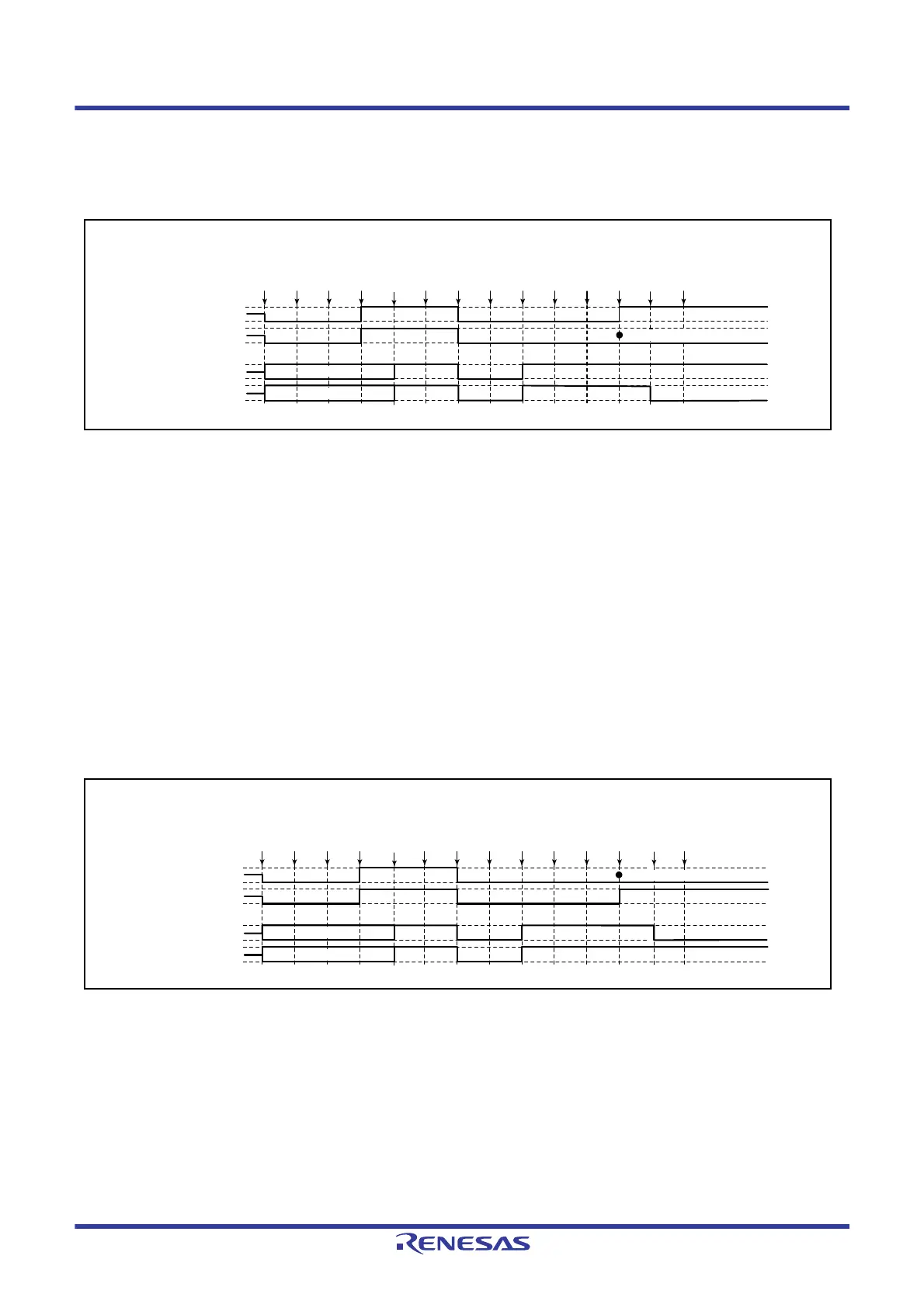

(3) Operation When Error Occurs in Normal Mode and Operation is Restarted in PWM Mode 2

Figure 23.118 shows a case in which an error occurs in normal mode and operation is restarted in PWM mode 2 after re-

setting.

Figure 23.118 Error Occurrence in Normal Mode, Recovery in PWM Mode 2

(1) to (10) are the same as in Figure 23.116.

(11) Set PWM mode 2.

(12) Initialize the pins with the TIOR register. (In PWM mode 2, the cycle register pins are not initialized. If

initialization is required, initialize in normal mode, then switch to PWM mode 2.)

(13) Use the MPC and the port mode register (PMR) for the I/O port to set up MTU output.

(14) Restart operation by setting the TSTR register.

Note: PWM mode 2 can only be selected for MTU0 to MTU2, and therefore the TOER register setting is not necessary.

(1)

Reset

(2)

TMDR

(normal)

(3)

TOER

(1)

(4)

TIOR

(1 init

0 out)

(6)

TSTR

(1)

(7)

Match

(8)

Error

occurs

(9)

Port

output

(10)

TSTR

(0)

(11)

TMDR

(PWM1)

(12)

TIOR

(1 init

0 out)

(14)

TSTR

(1)

(5)

MPC

(MTU)

(13)

MPC

(MTU)

MTU module output

MTIOCnA

MTIOCnB

PORT output

Pxx

Pxx

Hi-Z

Hi-Z

Not initialized (MTIOCnB)

(1)

Reset

(2)

TMDR

(normal)

(3)

TOER

(1)

(4)

TIOR

(1 init

0 out)

(6)

TSTR

(1)

(7)

Match

(8)

Error

occurs

(9)

Port

output

(10)

TSTR

(0)

(11)

TMDR

(PWM2)

(12)

TIOR

(1init

0 out)

(14)

TSTR

(1)

(5)

MPC

(MTU)

(13)

MPC

(MTU)

MTU module output

MTIOCnA

MTIOCnB

PORT output

Pxx

Pxx

Hi-Z

Hi-Z

Not initialized (cycle register)

Loading...

Loading...