R01UH0823EJ0100 Rev.1.00 Page 865 of 1823

Jul 31, 2019

RX23W Group 32. USB 2.0 Host/Function Module (USBc)

D0FIFOSEL, D1FIFOSEL

Note 1. Only 0 can be read.

The same pipe should not be specified by the CURPIPE[3:0] bits in the CFIFOSEL, D0FIFOSEL, and D1FIFOSEL

registers. When the CURPIPE[3:0] bits in the D0FIFOSEL and D1FIFOSEL registers are set to 0000b, no pipe is

selected.

The pipe number should not be changed while the DMA/DTC transfer is enabled.

Address(es): D0FIFOSEL 000A 0028h, D1FIFOSEL 000A 002Ch

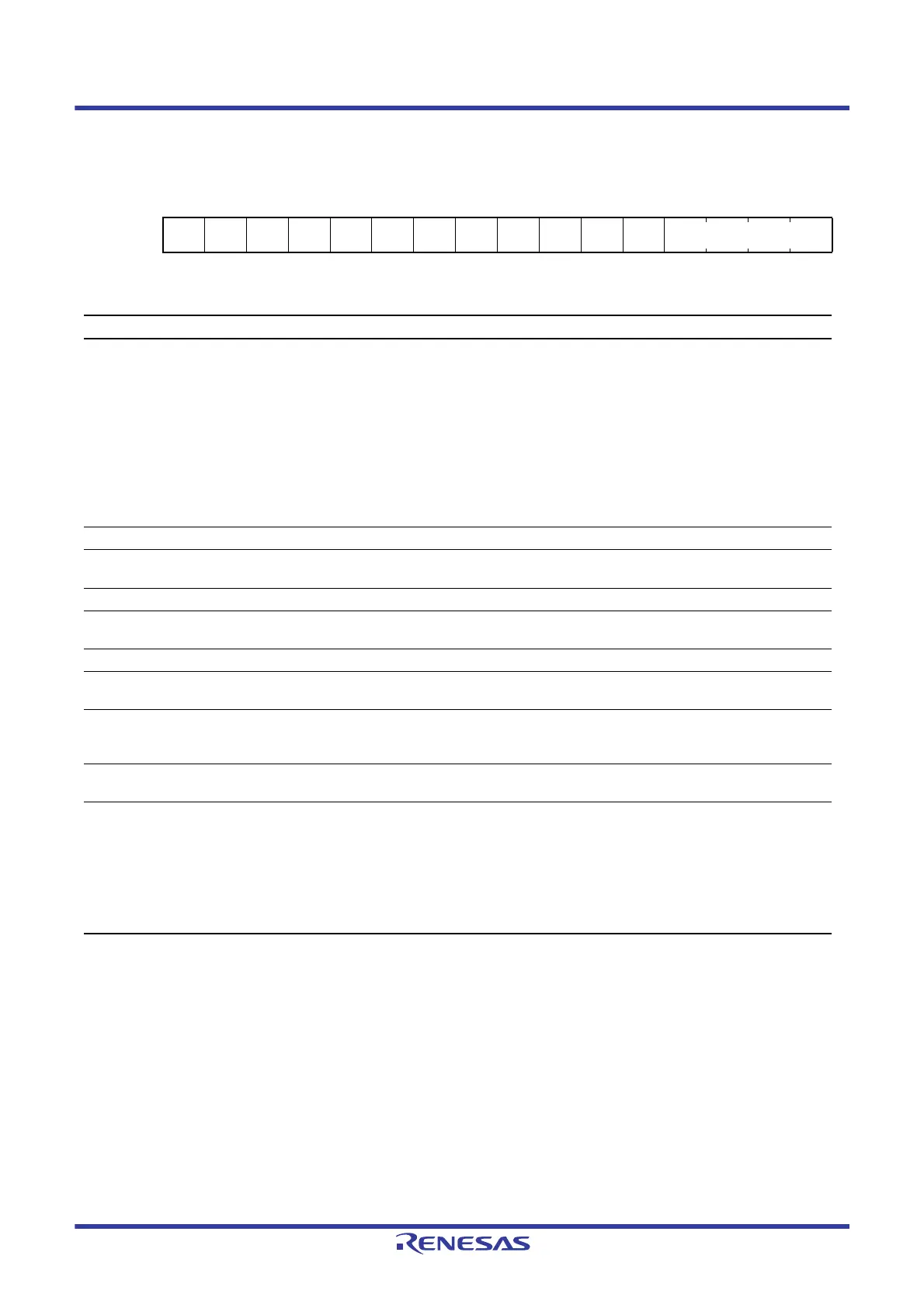

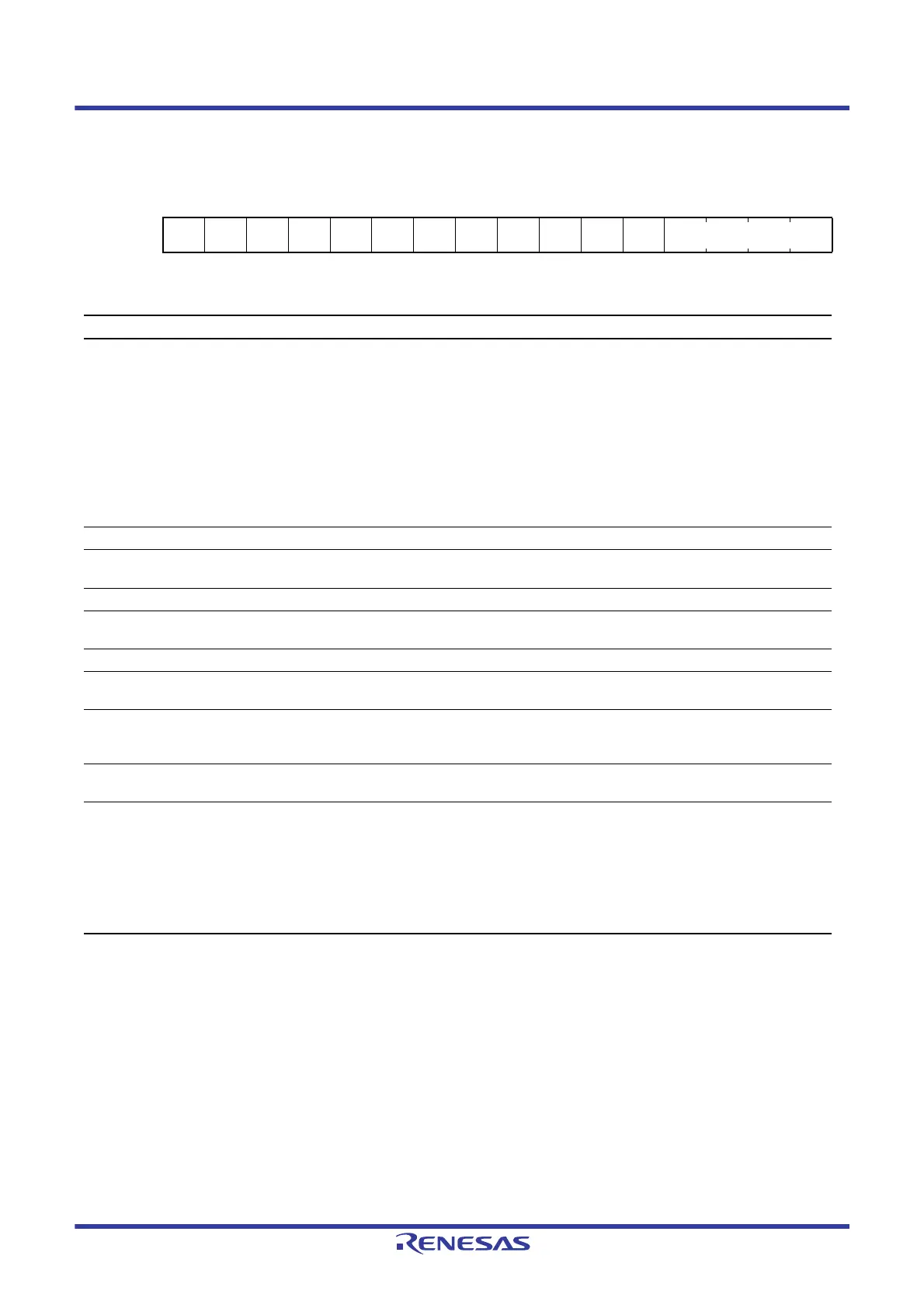

b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

RCNT REW DCLRM DREQE — MBW —

BIGEN

D

———— CURPIPE[3:0]

Value after reset:

0000000000000000

Bit Symbol Bit Name Description R/W

b3 to b0 CURPIPE

[3:0]

FIFO Port Access Pipe

Specification

b3 b0

0 0 0 0: DCP (Default control pipe)

0 0 0 1: Pipe 1

0 0 1 0: Pipe 2

0 0 1 1: Pipe 3

0 1 0 0: Pipe 4

0 1 0 1: Pipe 5

0 1 1 0: Pipe 6

0 1 1 1: Pipe 7

1 0 0 0: Pipe 8

1 0 0 1: Pipe 9

Settings other than above are prohibited.

R/W

b7 to b4 — Reserved These bits are read as 0. The write value should be 0. R/W

b8 BIGEND FIFO Port Endian Control 0: Little endian

1: Big endian

R/W

b9 — Reserved This bit is read as 0. The write value should be 0. R/W

b10 MBW FIFO Port Access Bit Width 0: 8-bit width

1: 16-bit width

R/W

b11 — Reserved This bit is read as 0. The write value should be 0. R/W

b12 DREQE DMA/DTC Transfer Request

Enable

0: DMA/DTC transfer request is disabled.

1: DMA/DTC transfer request is enabled.

R/W

b13 DCLRM Auto Buffer Memory Clear

Mode Accessed after

Specified Pipe Data is Read

0: Auto buffer clear mode is disabled.

1: Auto buffer clear mode is enabled.

R/W

b14 REW Buffer Pointer Rewind 0: The buffer pointer is not rewound.

1: The buffer pointer is rewound.

R/W

*1

b15 RCNT Read Count Mode 0: The DTLN[8:0] flags (CFIFOCTR.DTLN[8:0],

D0FIFOCTR.DTLN[8:0], D1FIFOCTR.DTLN[8:0]) are cleared

when all of the receive data has been read from the DnFIFO.

(In double buffer mode, the DTLN bit Value is cleared when all the

data has been read from only a single plane.)

1: The DTLN[8:0] flags are decremented each time the receive data

is read from the DnFIFO.

(n = 0, 1)

R/W

Loading...

Loading...