R01UH0823EJ0100 Rev.1.00 Page 995 of 1823

Jul 31, 2019

RX23W Group 33. Serial Communications Interface (SCIg, SCIh)

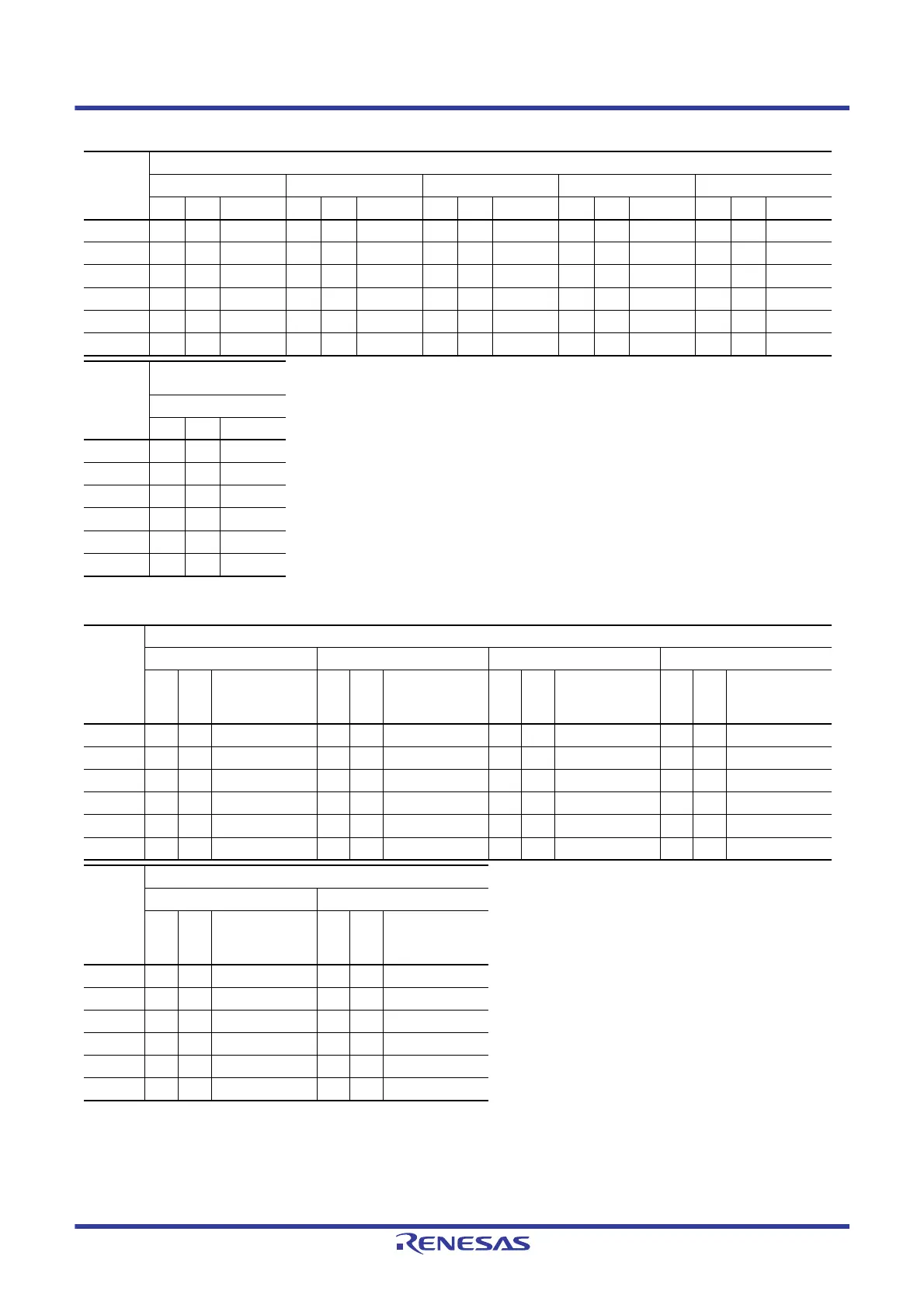

Table 33.22 BRR Settings for Various Bit Rates (Simple I

2

C Mode)

Bit Rate

(bps)

Operating Frequency PCLK (MHz)

8 10162025

n N Error (%) n N Error (%) n N Error (%) n N Error (%) n N Error (%)

10 k 0 24 0.0 0 31 –2.3 1 12 –3.8 1 15 –2.3 1 19 –2.3

25 k 0 9 0.0 0 12 –3.8 1 4 0.0 1 6 –10.7 1 7 –2.3

50 k 0 4 0.0 0 6 –10.7 1 2 –16.7 1 3 –21.9 1 3 –2.3

100 k 0 2 –16.7 0 3 –21.9 0 4 0.0 0 6 –10.7 1 1 –2.3

250 k 0 0 0.0 0 1 –37.5 0 1 0.0 0 2 –16.7 0 3 –21.9

350 k 0 1 –10.7 0 2 –25.6

Bit Rate

(bps)

Operating Frequency

PCLK (MHz)

30

n N Error (%)

10 k 1 23 –2.3

25 k 1 9 –6.3

50 k 1 4 –6.3

100 k 1 2 –21.9

250 k 0 3 –6.3

350 k 0 2 –10.7

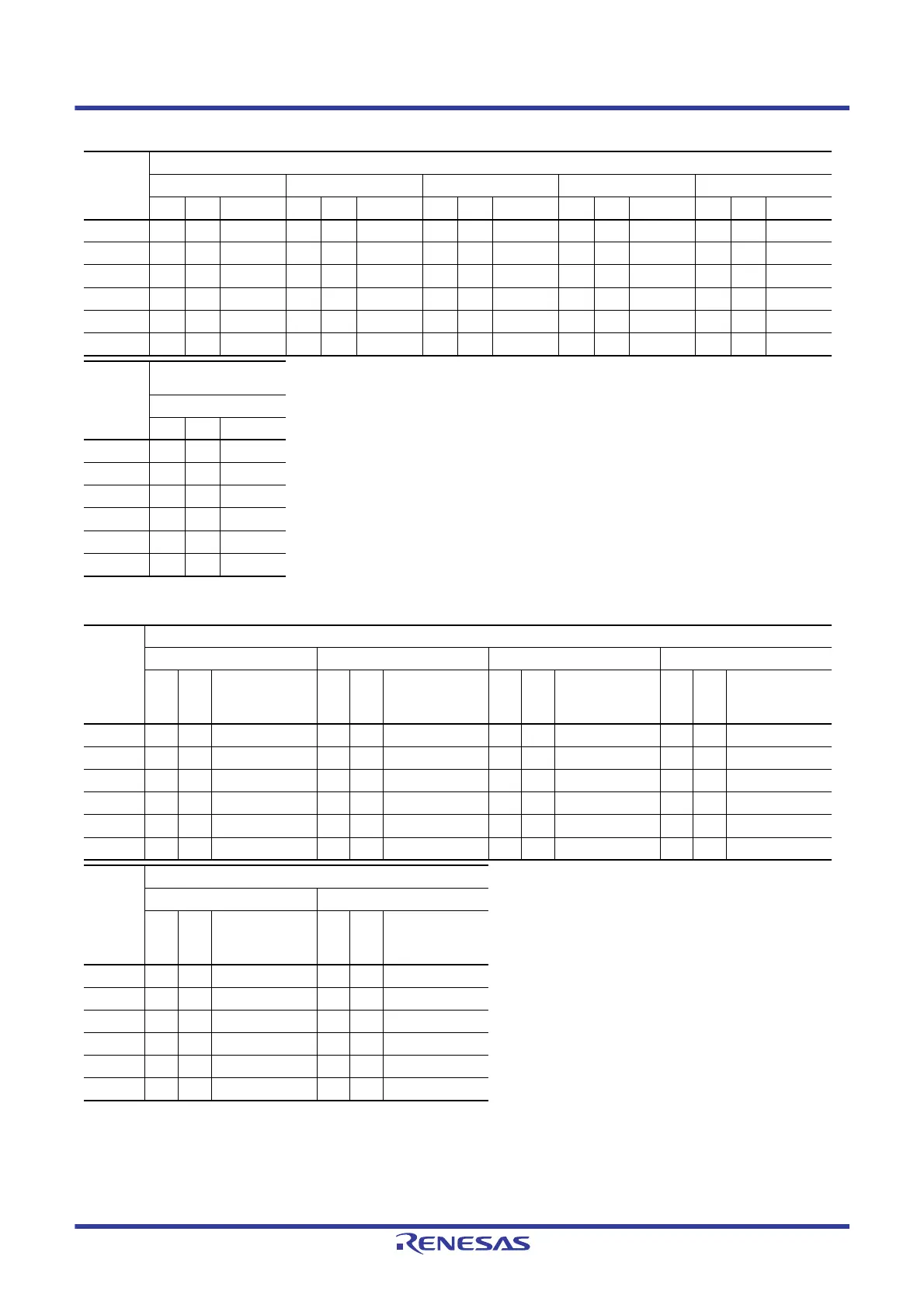

Table 33.23 Minimum Widths at High and Low Level for SCL at Various Bit Rates (Simple I

2

C Mode)

Bit Rate

(bps)

Operating Frequency PCLK (MHz)

8101620

nN

Min. Widths at

High/Low Level

for SCL (μs) n N

Min. Widths at

High/Low Level

for SCL (μs) n N

Min. Widths at

High/Low Level

for SCL (μs) n N

Min. Widths at

High/Low Level

for SCL (μs)

10 k 0 24 43.75/50.00 0 31 44.80/51.20 1 12 45.50/52.00 1 15 44.80/51.20

25 k 0 9 17.50/20.00 0 12 18.20/20.80 1 4 17.50/20.00 1 6 19.60/22.40

50 k 0 4 8.75/10.00 0 6 9.80/11.20 1 2 10.50/12.00 1 3 11.20/12.80

100 k 0 2 5.25/6.00 0 3 5.60/6.40 0 4 4.37/5.00 0 6 4.90/5.60

250 k 0 0 1.75/2.00 0 1 2.80/3.20 0 1 1.75/2.00 0 2 2.10/2.40

350 k 0 1 1.40/1.60

Bit Rate

(bps)

Operating Frequency PCLK (MHz)

25 30

nN

Min. Widths at

High/Low Level

for SCL (μs) n N

Min. Widths at

High/Low Level

for SCL (μs)

10 k 1 19 44.80/51.20 1 23 44.80/51.20

25 k 1 7 17.92/20.48 1 9 18.66/21.33

50 k 1 3 8.96/10.24 1 4 9.33/10.66

100 k 1 1 4.48/5.12 1 2 5.60/6.40

250 k 0 3 2.24/2.56 0 3 1.86/2.13

350 k 0 2 1.68/1.92 0 2 1.40/1.60

Loading...

Loading...