R01UH0823EJ0100 Rev.1.00 Page 1374 of 1823

Jul 31, 2019

RX23W Group 38. Serial Peripheral Interface (RSPIa)

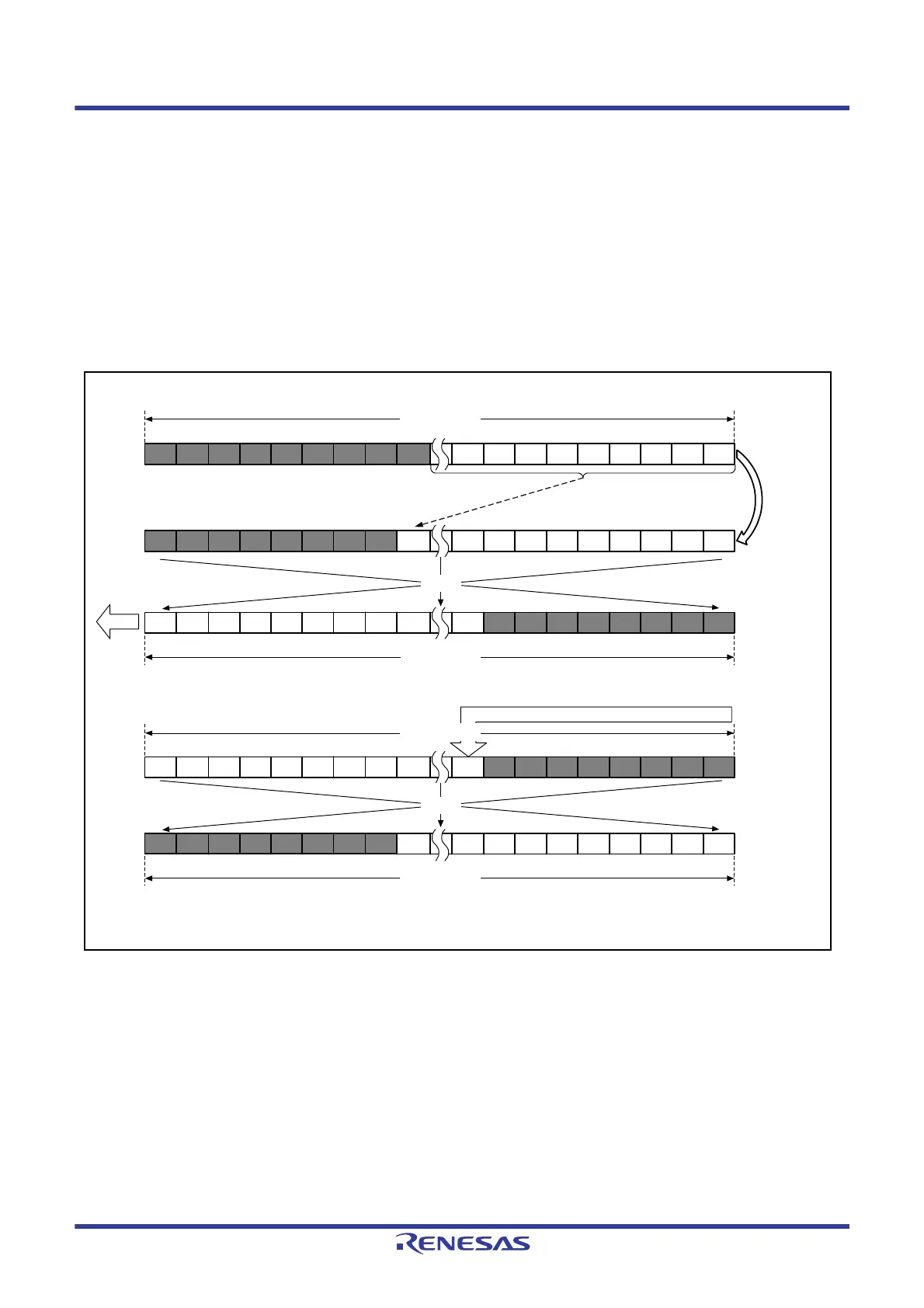

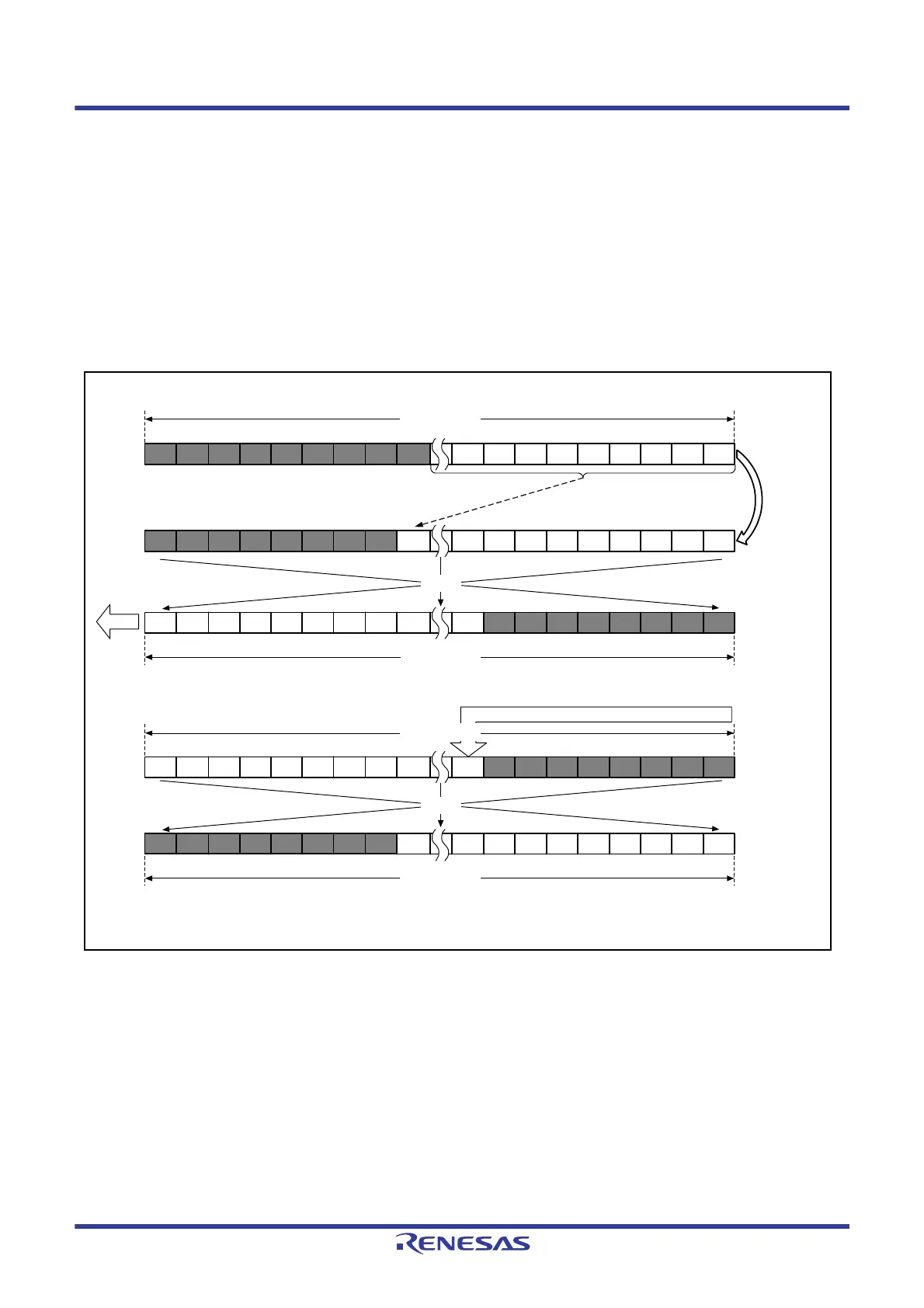

(4) LSB First Transfer (24-Bit Data)

Figure 38.21 shows details of operations by the RSPI data register (SPDR) and the shift register in transfer with parity

enabled, 24 bits as the RSPI data length for an example that is not 32 bits, and LSB first selected.

In transmission, the value of the parity bit (P) is calculated from bits T22 to T00. This replaces the final bit, T23, and the

whole is copied to the shift register. Data are transmitted in the order T00, T01, …, T22, and P.

In reception, received data are shifted in bit by bit through bit 8 of the shift register. When bits R00 to P have been

collected after input of the required number of cycles of RSPCK, the value in the shift register is copied to the receive

buffer. On copying of data to the shift register, the data from R00 to P are checked by judging the parity. At this time, the

higher-order 8 bits of the transmit buffer are stored in the higher-order 8 bits of the receive buffer. Writing 0 to bits T31

to T24 at the time of transmission leads to 0 being inserted in the higher-order 8 bits of the receive buffer.

Figure 38.21 LSB First Transfer (24-Bit Data, Parity Enabled)

Output

R00 R01 R02 R03 R04 R05 R06 R07 R08 T25 T26 T27 T28 T29 T30 T31

T31T30T29T28T27T26T25T24 P R06R05

PT24

R08 R07 R04 R03 R02 R01 R00

Input

Transfer start

Transfer end

Bit 31 Bit 0

T31 T30 T29 T28 T27 T26 T25 T24 T23 T06 T05 T04 T03 T02 T01 T00

T00T01T02T03T04T05T06T07T08 T25T26T27T28T29T30T31

T08 T07

PT24

Receive buffer

Transmit buffer

Shift register

Shift register

Copy

Copy

Bit 31 Bit 0

Bit 31 Bit 0

Bit 31 Bit 0

T31 T30 T29 T28 T27 T26 T25 T24 P T06 T05 T04 T03 T02 T01 T00

T08 T07

Bit 31

Bit 0

Parity calculated Parity added

Note: Output = MOSI (master)/MISO (slave), input = MISO (master)/MOSI (slave)

Loading...

Loading...