mode. For a description of how to set up the interrupt controller, DMAC, and I/O ports, refer to the descriptions given in

the individual blocks.

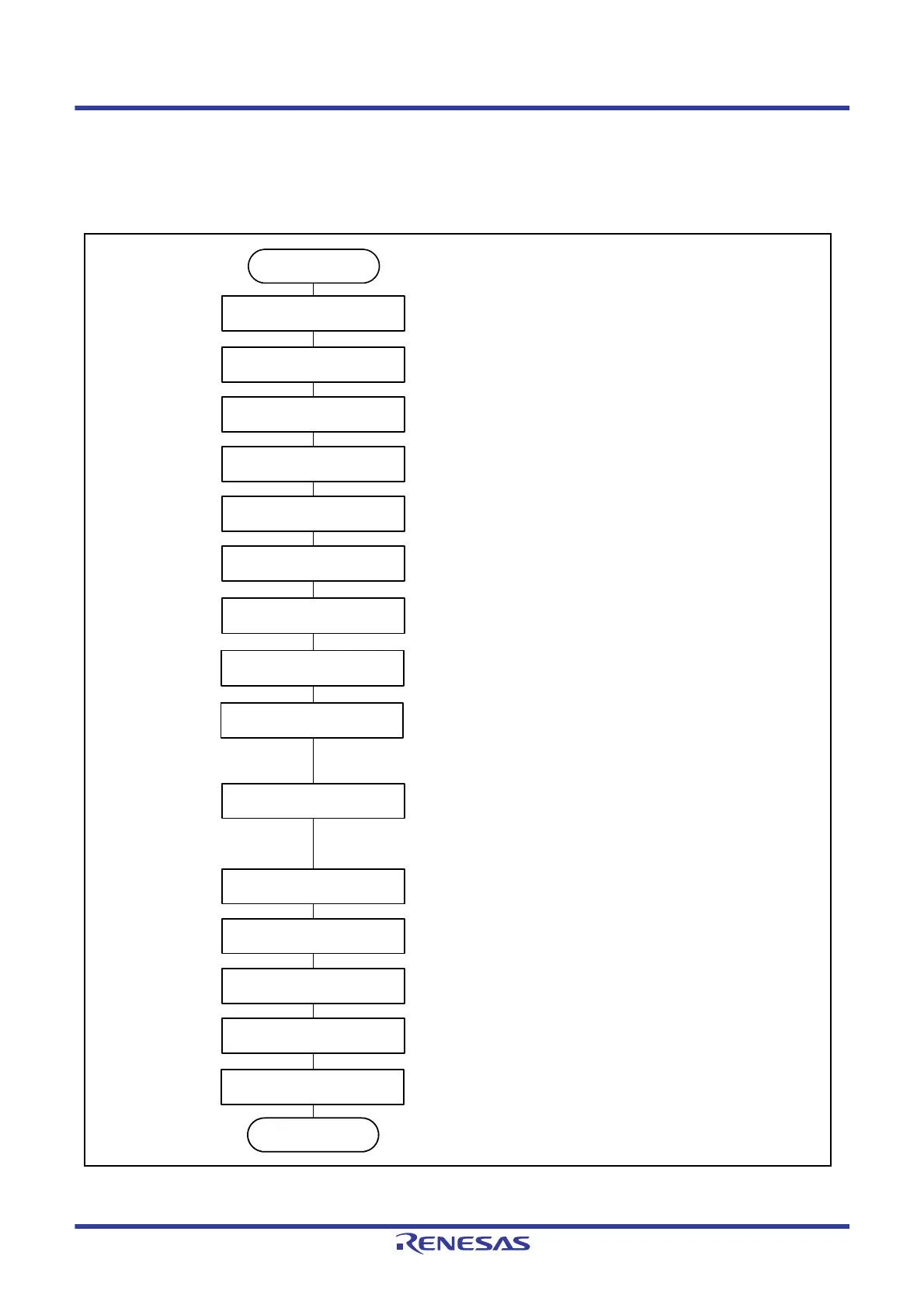

Set RSPI slave select polarity

register (SSLP)

Set RSPI bit rate register (SPBR)

Set RSPI data control register

(SPDCR)

Set RSPI clock delay register

(SPCKD)

Set RSPI slave select negation

delay register (SSLND)

Set RSPI next-access delay register

(SPND)

Set RSPI command registers 0 to 7

(SPCMD0 to SPCMD7)

Set I/O ports

Set RSPI control register (SPCR)

Set interrupt controller

Set DMAC

• Sets polarity of SSL signal.

• Sets next-access delay value.

(when using an interrupt)

• Sets transfer bit rate.

• Sets number of frames to be used.

• Sets RSPCK delay value.

• Sets SSL signal level.

• Sets RSPCK delay enable.

• Sets SSL negation delay enable.

• Sets next-access delay enable.

• Sets MSB or LSB first.

• Sets data length.

• Sets transfer bit rate.

• Sets clock phase.

• Sets clock polarity.

• Sets SSL assertion signal.

• Sets SSL negation delay value.

(when using the DMAC)

• Sets master mode.

• Sets interrupt mask.

• Sets RSPI mode.

Set RSPI control register 2 (SPCR2)

• Sets parity function.

• Sets interrupt mask.

Read RSPI control register (SPCR)

RSPI sequence control register

(SPSCR)

• Sets sequence length.

Set RSPI pin control register

(SPPCR)

• Sets output mode (CMOS/open-drain).

• Sets MOSI signal value when transfer is in idle state.

End of initialization in

master mode

Start of initialization in

master mode

Loading...

Loading...