R01UH0823EJ0100 Rev.1.00 Page 1392 of 1823

Jul 31, 2019

RX23W Group 38. Serial Peripheral Interface (RSPIa)

(7) Next-Access Delay (t3)

The next-access delay value of the RSPI in master mode depends on the SPCMDm.SPNDEN bit setting and the SPND

setting. The RSPI determines the SPCMDm register to be referenced during serial transfer by pointer control, and

determines a next-access delay value during serial transfer by using the SPCMDm.SPNDEN bit and SPND, as listed in

Table 38.11. For a definition of next-access delay, refer to section 38.3.5, Transfer Format.

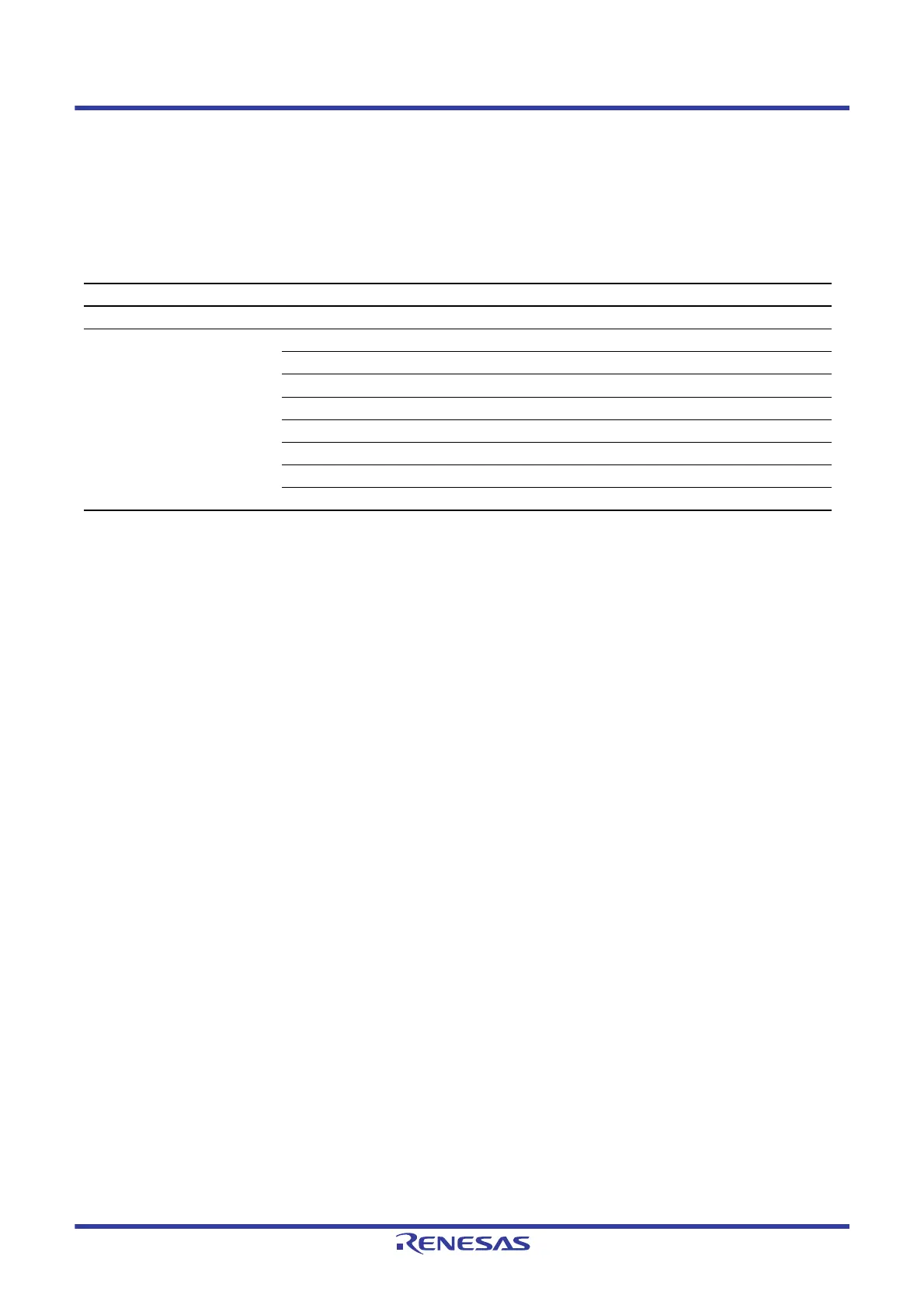

Table 38.11 Relationship among SPNDEN Bit, SPND, and Next-Access Delay Value

SPCMDm.SPNDEN Bit SPND.SPNDL[2:0] Bits Next-Access Delay Value

0 000b to 111b 1 RSPCK + 2 PCLK

1 000b 1 RSPCK + 2 PCLK

001b 2 RSPCK + 2 PCLK

010b 3 RSPCK + 2 PCLK

011b 4 RSPCK + 2 PCLK

100b 5 RSPCK + 2 PCLK

101b 6 RSPCK + 2 PCLK

110b 7 RSPCK + 2 PCLK

111b 8 RSPCK + 2 PCLK

Loading...

Loading...