R01UH0823EJ0100 Rev.1.00 Page 925 of 1823

Jul 31, 2019

RX23W Group 32. USB 2.0 Host/Function Module (USBc)

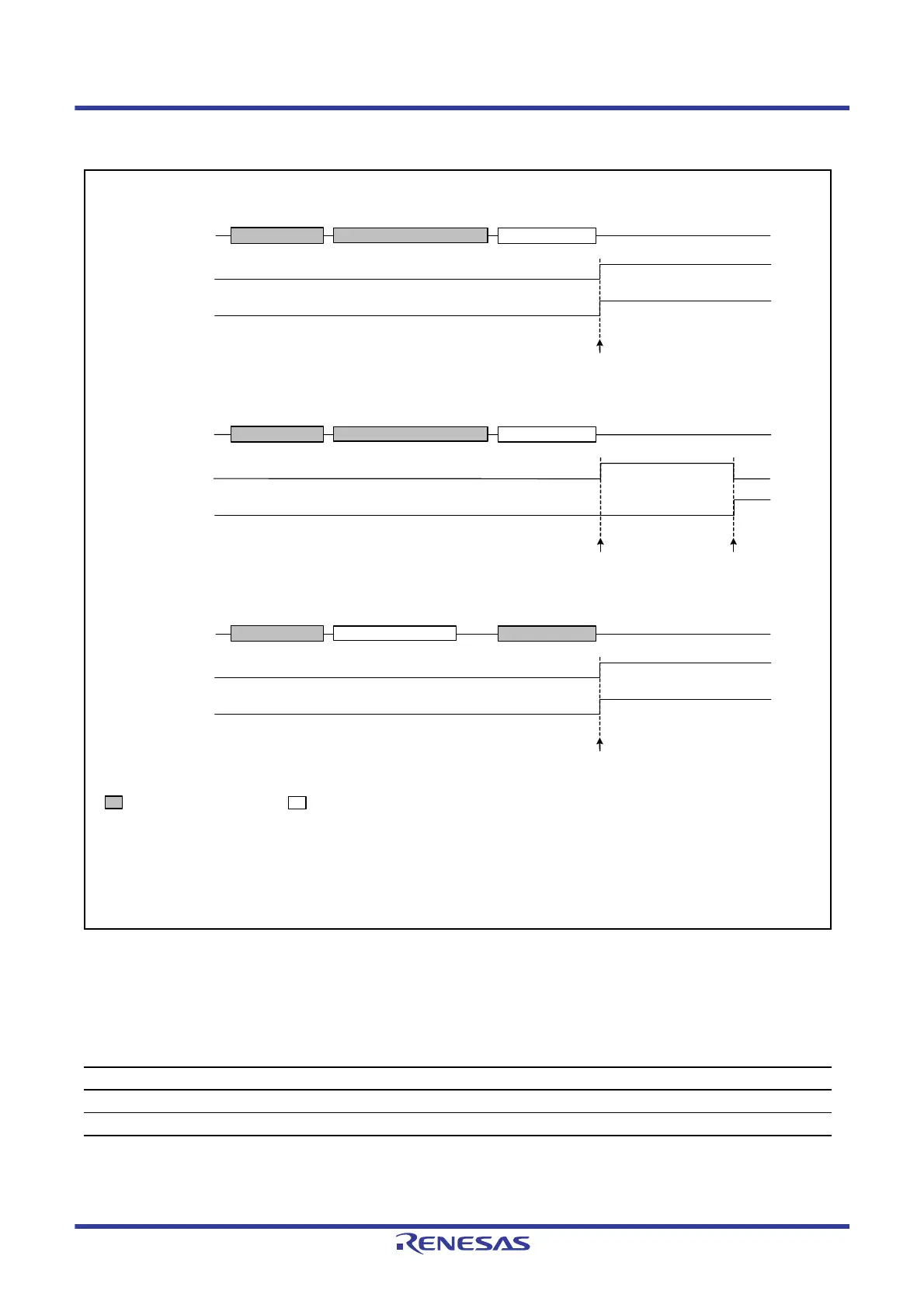

Figure 32.9 shows the timing of BRDY interrupt generation.

Figure 32.9 Timing of BRDY Interrupt Generation

The condition that USB clears the INTSTS0.BRDY flag depends on the SOFCFG.BRDYM bit setting. Table 32.14

shows the condition for clearing the BRDY flag.

Table 32.14 Condition for Clearing BRDY Flag

BRDYM Bit Condition for Clearing BRDY Flag

0 The USB sets the BRDY flag to 0 when all bits in the BRDYSTS register have been set to 0 by software.

1 The USB sets the BRDY flag to 0 when the BSTS flags for all pipes have become 0.

(3) Example of packet transmission (single-buffer mode)

Ready for transmission

Ready for write access

A BRDY interrupt is generated

because the FIFO buffer

becomes ready for write access.

Token Packet

ACK Handshake

Data Packet

(1) Example of zero-length packet reception or data packet reception when BFRE = 0 (single-buffer mode)

USB bus

FIFO buffer status

Ready for reception

Ready for read access

BRDY interrupt

(BRDYSTS.PIPEnBRDY flag)

A BRDY interrupt is generated because the

FIFO buffer becomes ready for read access.

*2

Token Packet

ACK Handshake

Data Packet

*1

(2) Example of data packet reception when BFRE = 1 (single-buffer mode)

Token Packet ACK Handshake

<Last> Data Packet

The FIFO buffer becomes

ready for read access.

*2

A BRDY interrupt is generated

because the transfer has ended.

*3

Note 1. The ACK handshake is not used in isochronous transfers.

Note 2. The FIFO buffer becomes ready for read access under the following condition:

When a packet is received while no data remains unread in the FIFO buffer in the CPU.

Note 3. A transfer ends under either of the following conditions:

(1) When a short packet including a zero-length packet is received

(2) When the number of packets specified in the transaction counter are received

Packet transmitted by host device

Packet transmitted by function device

USB bus

FIFO buffer status

BRDY interrupt

(BRDYSTS.PIPEnBRDY flag)

USB bus

FIFO buffer status

BRDY interrupt

(BRDYSTS.PIPEnBRDY flag)

*1

*1

Ready for reception

Ready for read access

Loading...

Loading...