R01UH0823EJ0100 Rev.1.00 Page 1030 of 1823

Jul 31, 2019

RX23W Group 33. Serial Communications Interface (SCIg, SCIh)

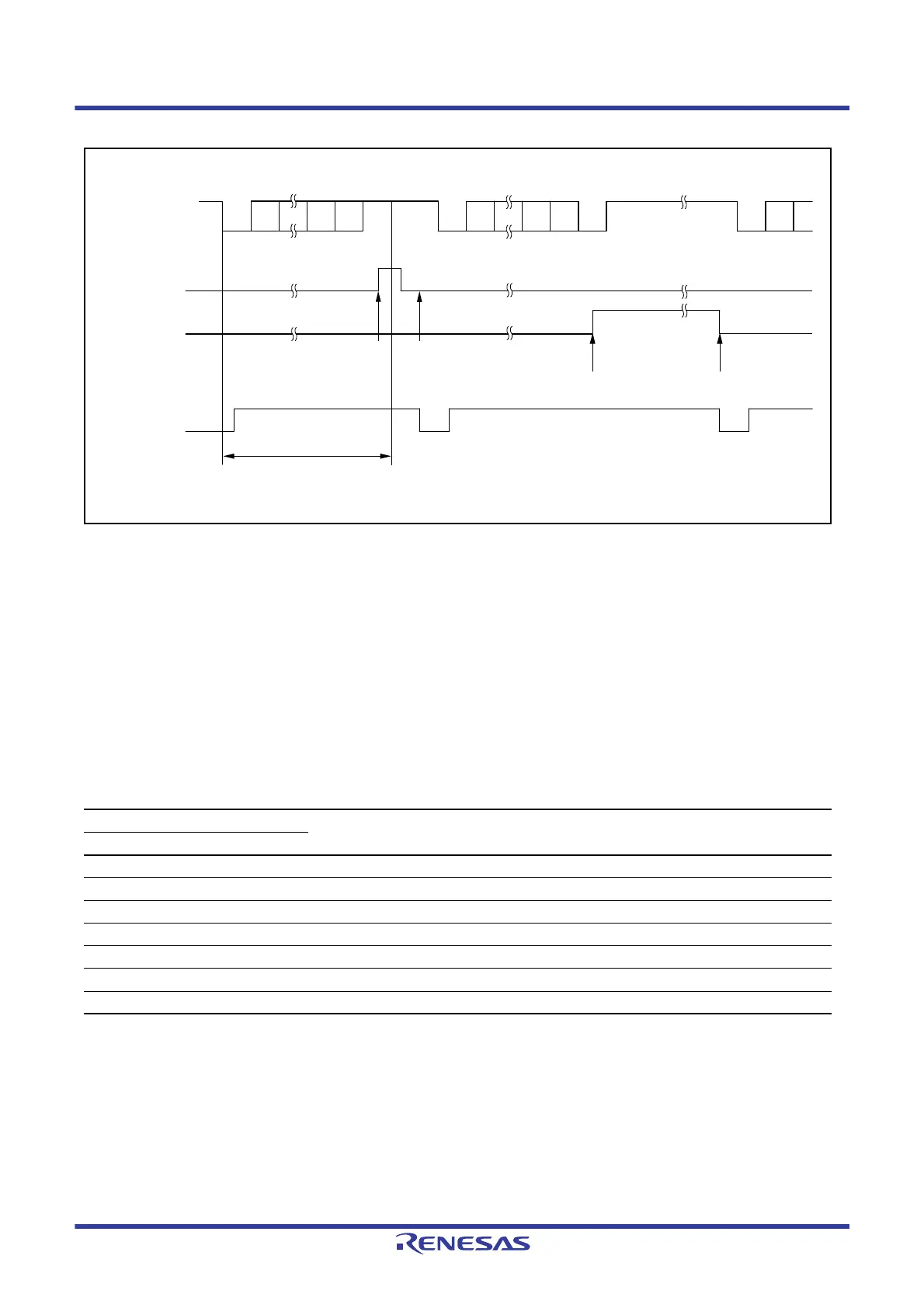

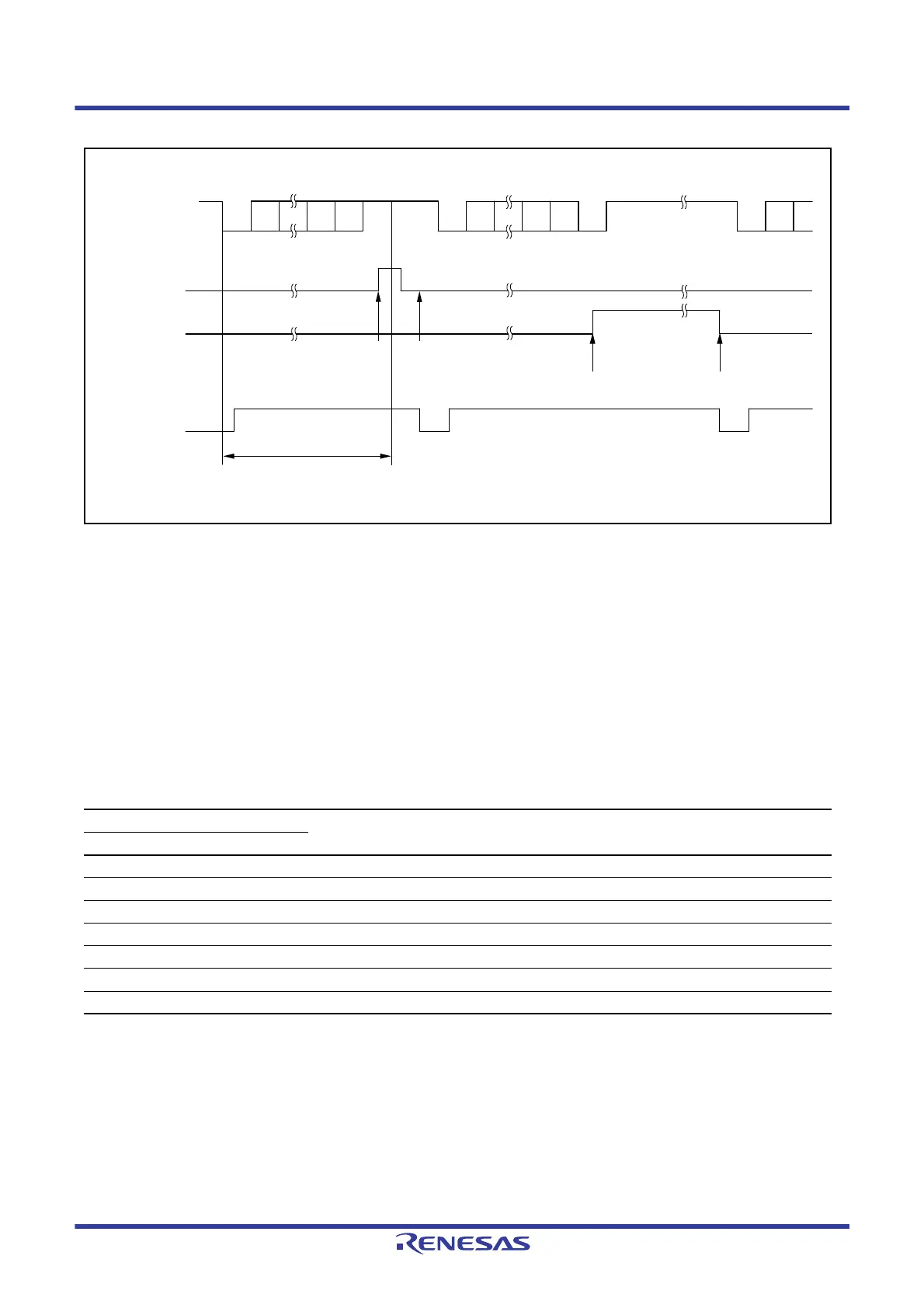

Figure 33.15 Example of SCI Operation for Serial Reception in Asynchronous Mode (2)

(When RTS Function is Used) (Example with 8-Bit Data, Parity, 1 Stop Bit)

Table 33.28 lists the states of the flags in the SSR status register and receive data handling when a receive error is

detected.

If a receive error is detected, an ERI interrupt request is generated but an RXI interrupt request is not generated. Data

reception cannot be resumed while the receive error flag is 1. Accordingly, set the ORER, FER, and PER flags to 0

before resuming reception. Moreover, be sure to read the RDR (or the RDRL) during overrun error processing. When a

reception is forcibly terminated by setting the SCR.RE bit to 0 during operation, read the RDR (or the RDRL) register

because received data which has not yet been read may be left in RDR (or the RDRL).

Figure 33.16 and Figure 33.17 show samples of flowcharts for serial data reception.

Note 1. Read data not in RDR but in the RDRH and RDRL registers when 9-bit data length is selected.

Table 33.28 Flags in the SSR Status Register and Receive Data Handling

Flags in the SSR Status Register

Receive Data Receive Error TypeORER FER PER

1 0 0 Lost Overrun error

010Transferred to RDR*

1

Framing error

001Transferred to RDR*

1

Parity error

1 1 0 Lost Overrun error + framing error

1 0 1 Lost Overrun error + parity error

011Transferred to RDR*

1

Framing error + parity error

1 1 1 Lost Overrun error + framing error + parity error

RXI interrupt flag

(IRn in ICU*

1

)

SSR.FER flag

0

1 frame

D0

D7 0/1 1 0 D0 D7

0/1 0

Data Data

Parity

bit

Stop

bit

Start bit

Parity

bit

Stop

bit

Start bit

Idle state

(mark state)

ERI interrupt request

generated by framing error

RXI interrupt

request

generated

RDR data read in RXI interrupt

handling routine

RTSn# pin

Error flag is cleared

0D0

Data

Start bit

Note 1. Refer to section 15, Interrupt Controller (ICUb) for details on the corresponding interrupt vector number.

Loading...

Loading...