Register Map

www.ti.com

100

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

Cortex

®

-M4 Peripherals

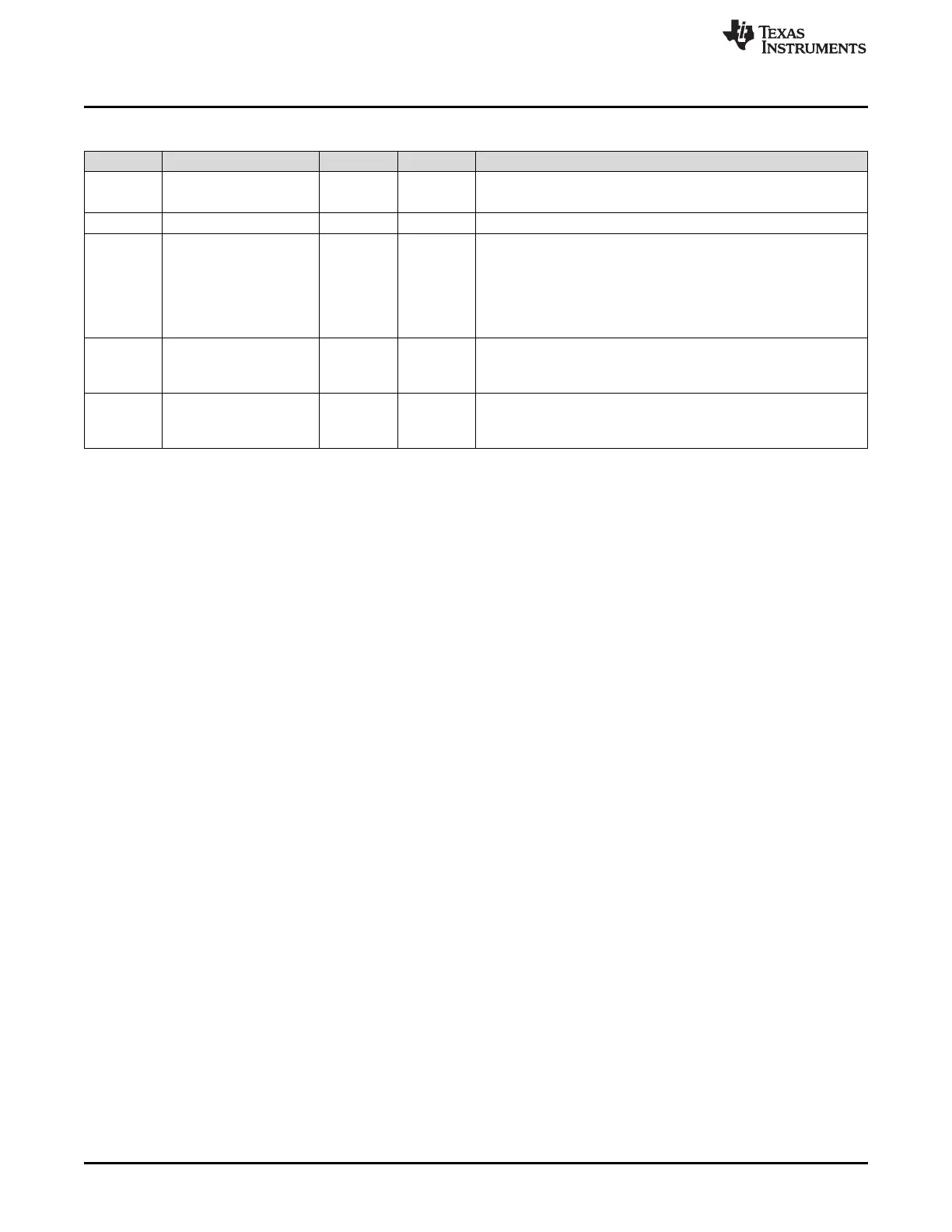

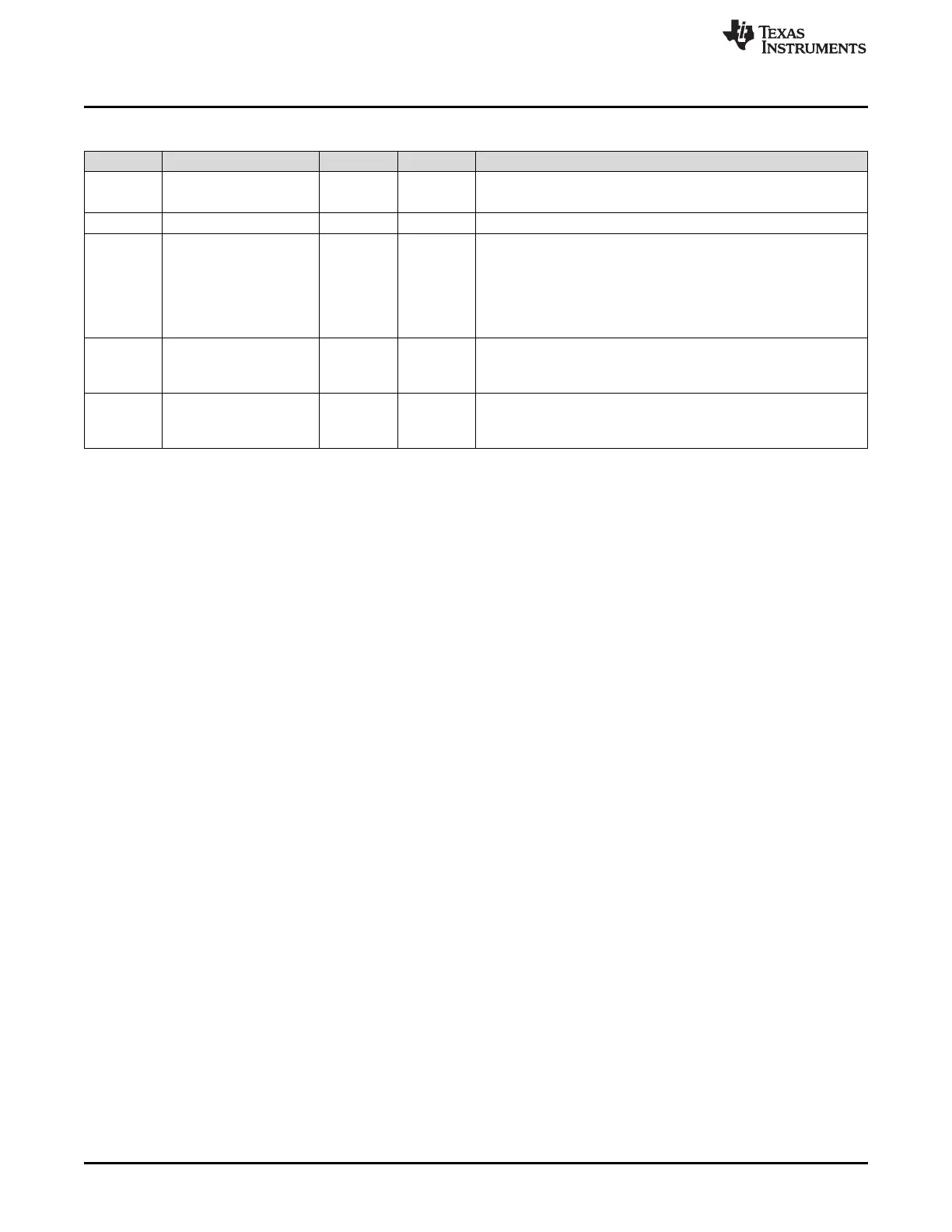

Table 3-17. APINT Register Field Descriptions (continued)

Bit Field Type Reset Description

10-8 PRIGROUP R/W 0h

Interrupt Priority Grouping

This field determines the split of group priority from subpriority

7-3 RESERVED R 0h

2 SYSRESREQ W 0h

System Reset Request

This bit is automatically cleared during the reset of the core and

reads as 0.

0h = No effect.

1h = Resets the core and all on-chip peripherals except the Debug

interface.

1 VECTCLRACT W 0h

Clear Active NMI / Fault

This bit is reserved for debug use and reads as 0. This bit must be

written as a 0, otherwise behavior is unpredictable.

0 VECTRESET W 0h

System Reset

This bit is reserved for debug use and reads as 0. This bit must be

written as a 0, otherwise behavior is unpredictable.

Loading...

Loading...