Flash Registers

www.ti.com

770

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

On-Chip Parallel Flash

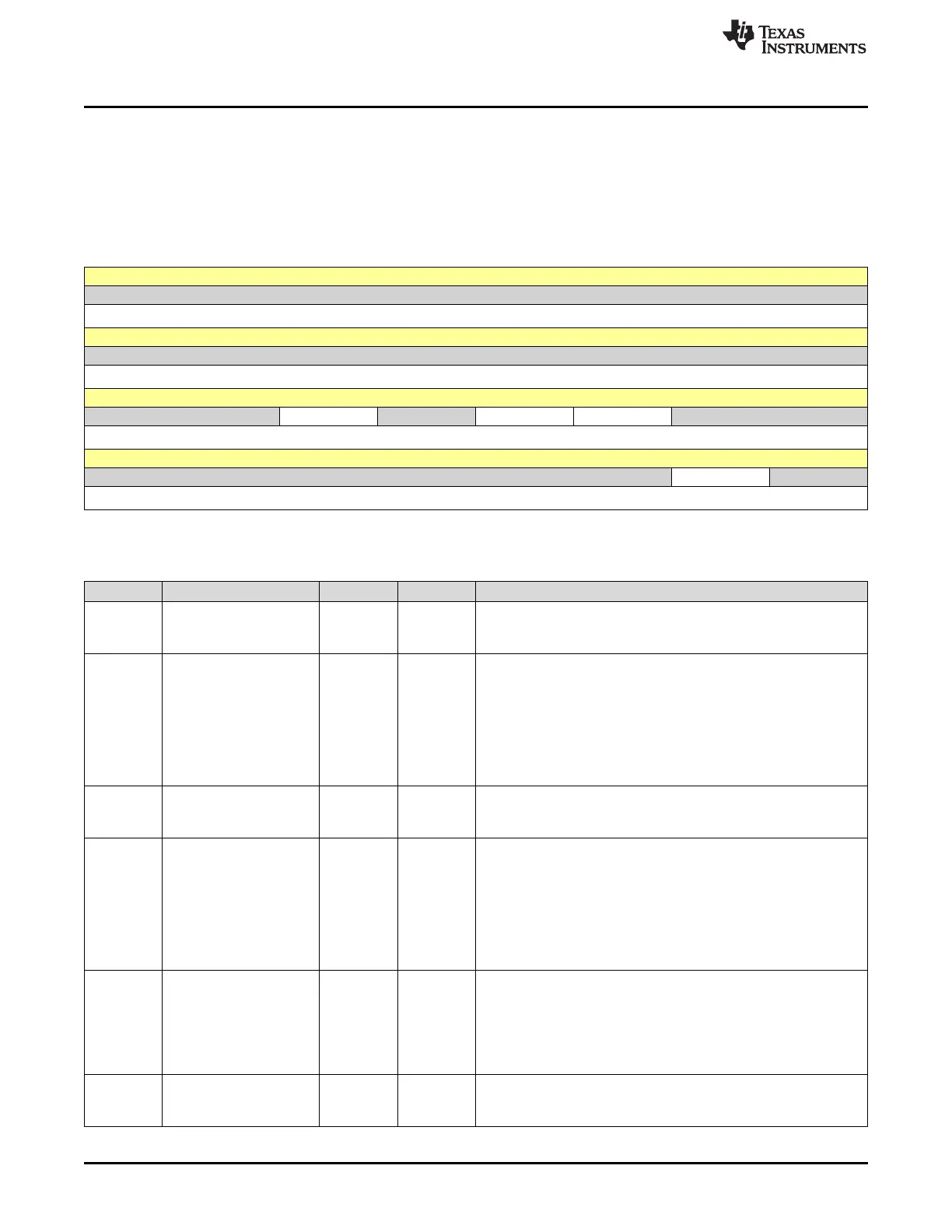

21.5.4 FCRIS Register (Offset = Ch) [reset = 0h]

FCRIS is shown in Figure 21-4 and described in Table 21-5.

Return to Summary Table.

This register indicates that the flash memory controller has an interrupt condition. An interrupt is sent to

the interrupt controller only if the corresponding FCIM register bit is set.

Figure 21-4. FCRIS Register

31 30 29 28 27 26 25 24

RESERVED

R-0h

23 22 21 20 19 18 17 16

RESERVED

R-0h

15 14 13 12 11 10 9 8

RESERVED PROGRIS RESERVED ERRIS INVDRIS RESERVED

R-0h R-0h R-0h R-0h R-0h R-0h

7 6 5 4 3 2 1 0

RESERVED PRIS RESERVED

R-0h R-0h R-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

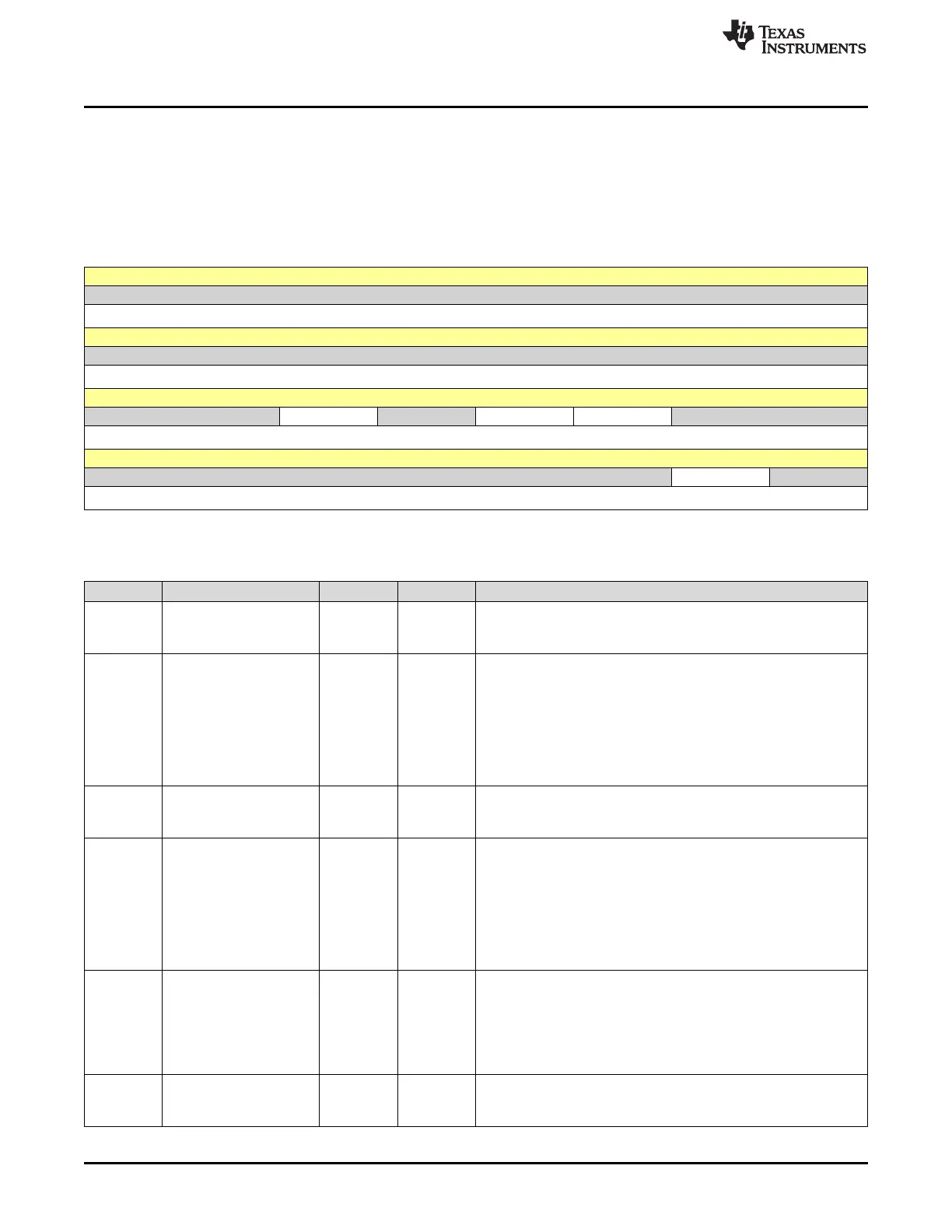

Table 21-5. FCRIS Register Field Descriptions

Bit Field Type Reset Description

31-14 RESERVED R 0h

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should

be preserved across a read-modify-write operation.

13 PROGRIS R 0h

Program Verify Error Raw Interrupt Status

This bit is cleared by writing 1 to the PROGMISC bit in the FCMISC

register.

0h = An interrupt has not occurred.

1h = An interrupt is pending because the verification of a PROGRAM

operation failed. If this error occurs when using the flash write buffer,

software must inspect the affected words to determine where the

error occurred.

12 RESERVED R 0h

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should

be preserved across a read-modify-write operation.

11 ERRIS R 0h

Erase Verify Error Raw Interrupt Status

This bit is cleared by writing 1 to the ERMISC bit in the FCMISC

register.

0h = An interrupt has not occurred.

1h = An interrupt is pending because the verification of an ERASE

operation failed. If this error occurs when using the flash write buffer,

software must inspect the affected words to determine where the

error occurred.

10 INVDRIS R 0h

Invalid Data Raw Interrupt Status

This bit is cleared by writing 1 to the INVMISC bit in the FCMISC

register.

0h = An interrupt has not occurred.

1h = An interrupt is pending because a bit that was previously

programmed as 0 is now being requested to be programmed as 1.

9-2 RESERVED R 0h

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should

be preserved across a read-modify-write operation.

Loading...

Loading...