www.ti.com

Timer Registers

343

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

General-Purpose Timers

9.5.19 GPTMTAV Register (offset = 50h) [reset = FFFFFFFFh]

GPTMTAV is shown in Figure 9-23 and described in Table 9-27.

When a 16/32-bit GPTM is configured to one of the 32-bit modes, GPTMTAV appears as a 32-bit register

(the upper 16 bits correspond to the contents of the GPTM Timer B Value (GPTMTBV) register). In a 16-

bit mode, bits 15:0 contain the value of the counter and bits 23:16 contain the current, free-running value

of the prescaler, which is the upper 8 bits of the count in input edge-count, input edge-time, PWM, and

one-shot or periodic up count modes. In one-shot or periodic down count modes, the prescaler stored in

23:16 is a true prescaler, meaning bits 23:16 count down before decrementing the value in bits 15:0. The

prescaler in bits 31:24 always reads as 0.

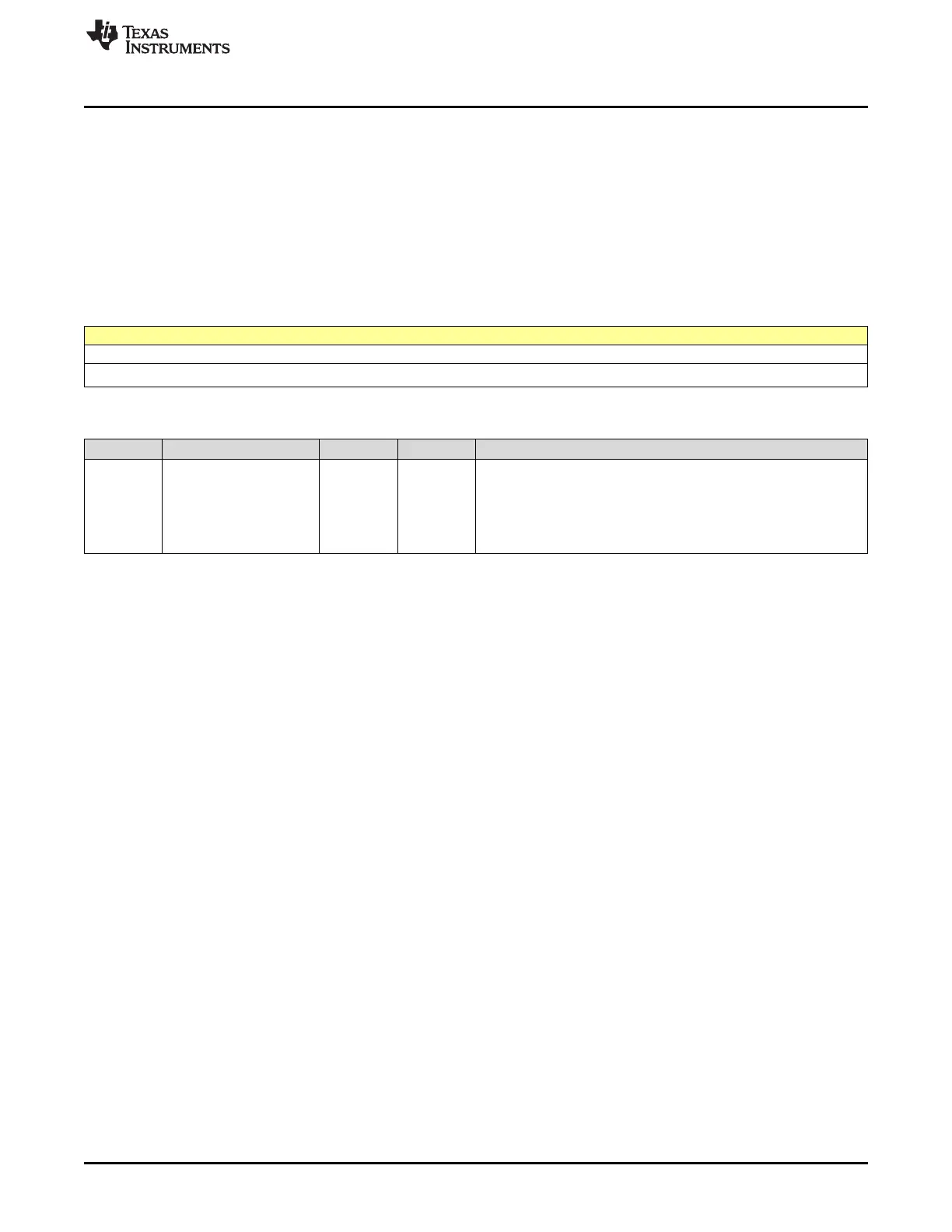

Figure 9-23. GPTMTAV Register

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

TAV

R/W-FFFFFFFFh

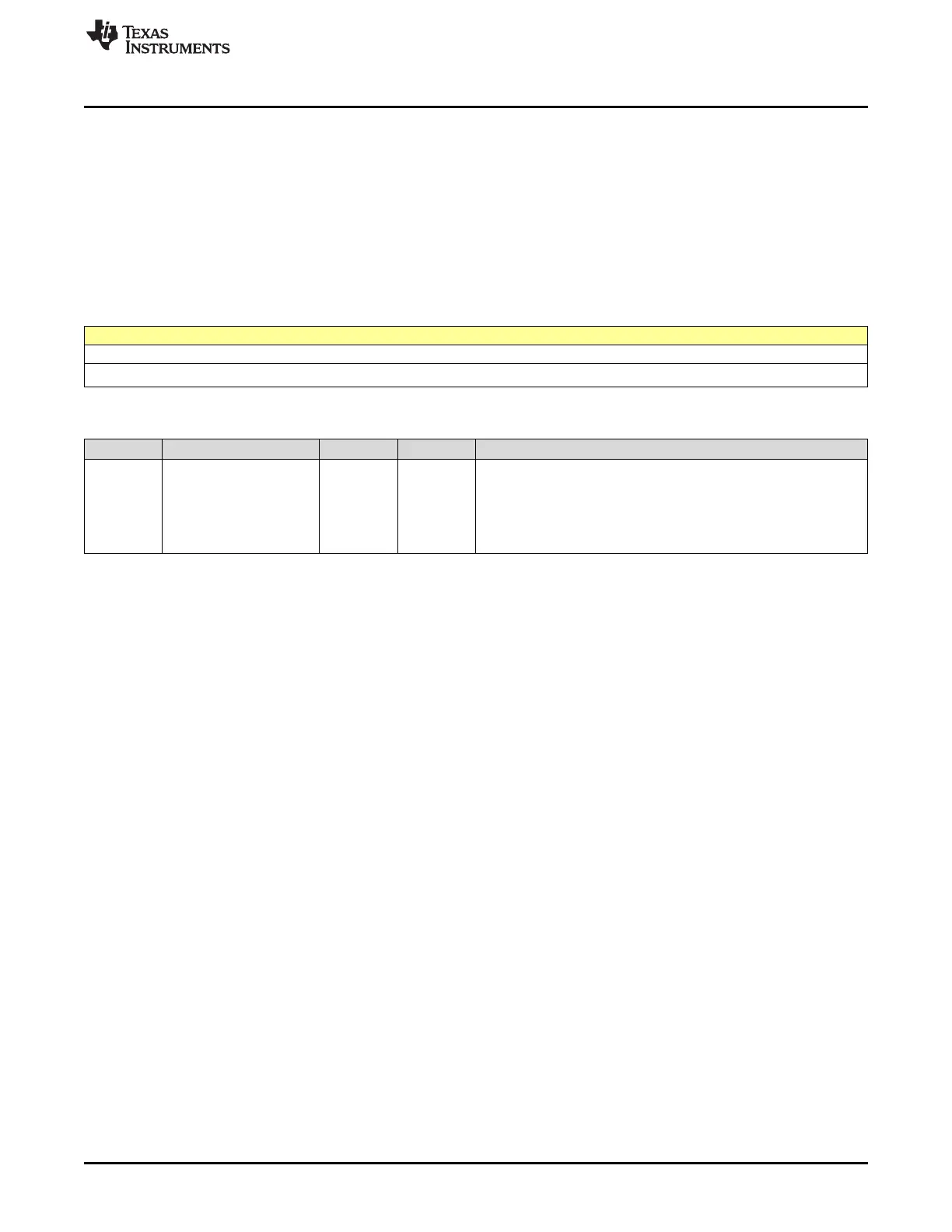

Table 9-27. GPTMTAV Register Field Descriptions

Bit Field Type Reset Description

31-0 TAV R/W FFFFFFFFh

GPTM Timer A Value. A read returns the current, free-running value

of Timer A in all modes. When written, the value written into this

register is loaded into the GPTMTAR register on the next clock

cycle. Note: In 16-bit mode, only the lower 16 bits of the GPTMTAV

register can be written with a new value. Writes to the prescaler bits

have no effect.

Loading...

Loading...