www.ti.com

Functional Description

273

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

SPI (Serial Peripheral Interface)

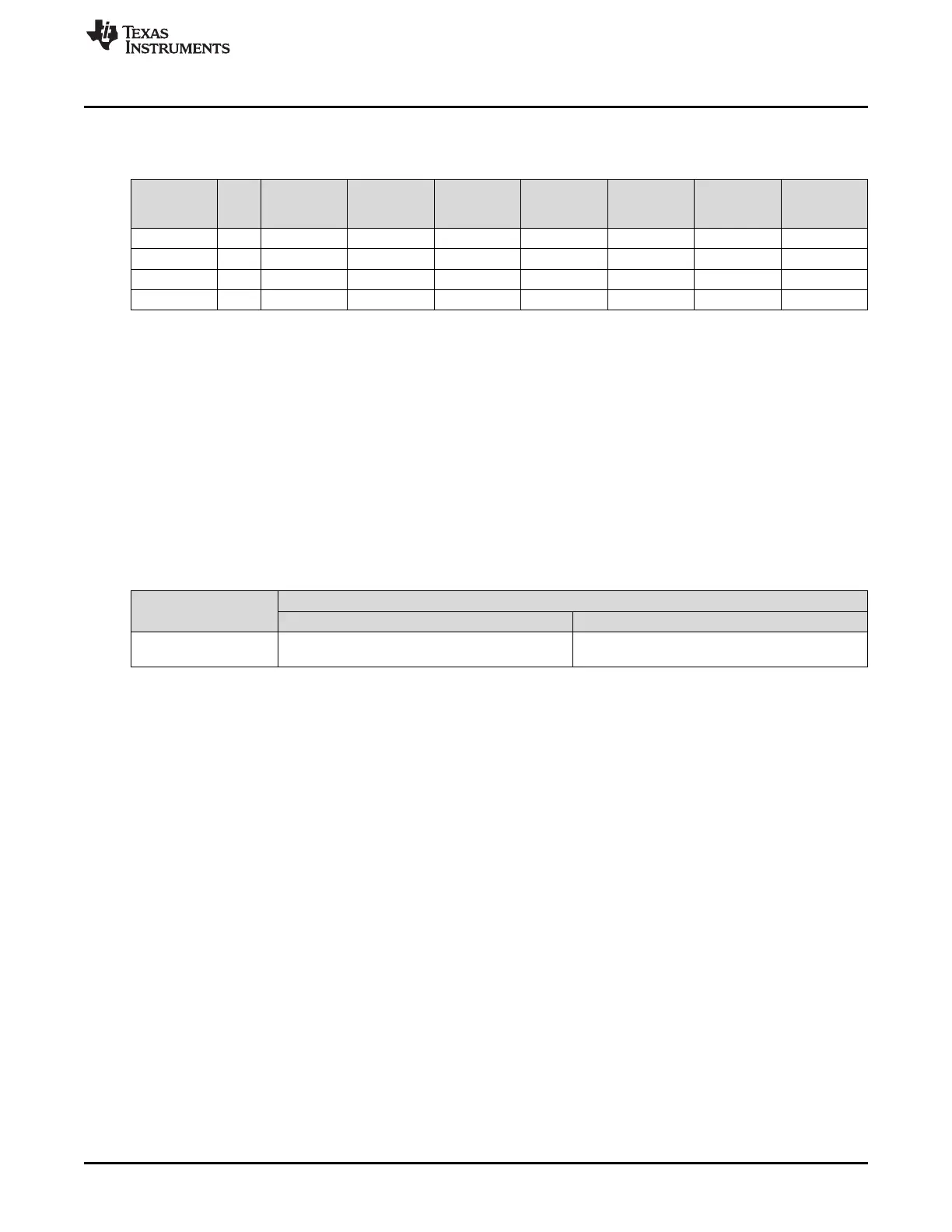

Table 8-4 lists granularity examples with a clock source frequency of 48 MHz.

Table 8-4. Granularity Examples

MCSPI_CHC

ONF

[CLKD]

F

ratio

MCSPI_CHC

ONF

[PHA]

MCSPI_CHC

ONF

[POL]

T

high

(ns)

T

low

(ns)

T

period

(ns)

Duty Cycle

F

out

(MHz)

0 1 X X 10.4 10.4 20.8 50-50 48

1 2 X X 20.8 20.8 41.6 50-50 24

2 4 X X 41.6 41.6 83.2 50-50 12

3 8 X X 83.2 83.2 166.4 50-50 6

8.2.3.4.1 FIFO Buffer Management

The SPI controller has a built-in 64-byte buffer to unload the DMA or interrupt handler and improve data

throughput. This buffer can be used by setting MCSPI_CHCONF[FFER] [FFRE]? See figs. 6 to 9. or

MCSPI_CHCONF[FFEW] [FFWE]? See figs. 6 to 9. to 1. The buffer can be used in the following modes:

• Master or slave mode

• Every word length MCSPI_CHCONF[WL] are supported.

Two levels, AEL and AFL, in the MCSPI_XFERLEVEL register, rule the buffer management. The driver

must set these values as a multiple of SPI word length defined in MCSPI_CHCONF[WL]. The number of

bytes written in the FIFO depends on word length (see Table 8-5). The FIFO buffer pointers are reset

when the channel is enabled, or when the FIFO configuration changes.

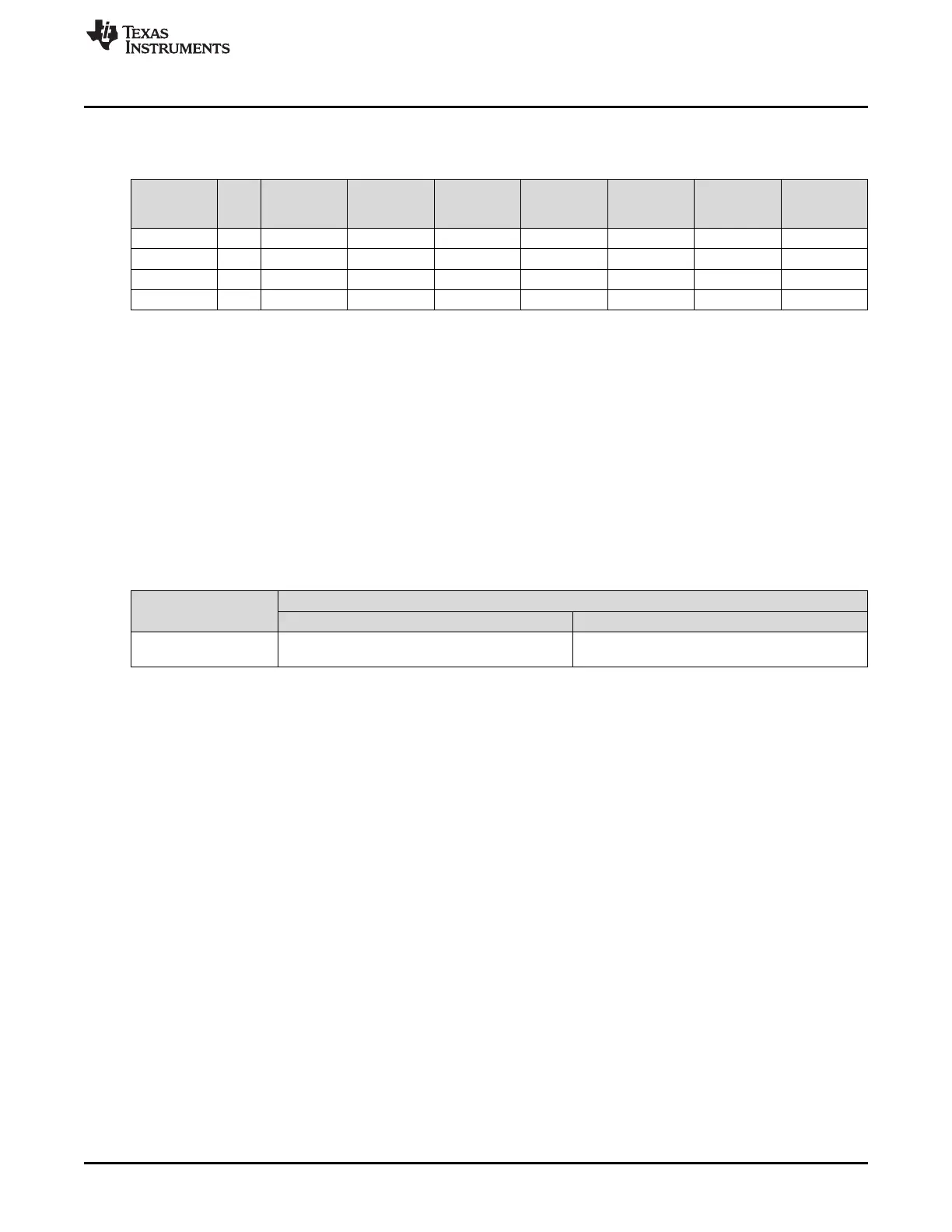

Table 8-5. SPI Word Length WL

SPI Word Length

8 16 and 32

Number of bytes written

in the FIFO

2 bytes 4 bytes

8.2.3.4.1.1 Split FIFO

The FIFO can be split into two parts when the module is configured in transmit/receive mode,

MCSPI_CHCONF[TRM] set to 0, and MCSPI_CHCONF[FFER] [FFRE]? See figs. 6 to 9.and

MCSPI_CHCONF[FFEW] [FFWE]? See figs. 6 to 9. are asserted. Then the system can access a 32-

byte-deep FIFO per direction. See Figure 8-7, Figure 8-8, Figure 8-9, and Figure 8-10.

Loading...

Loading...