Functional Description

www.ti.com

754

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

Cyclical Redundancy Check (CRC)

20.1.1.3 Endian Configuration

The following endian configuration is provided by the ENDIAN field in the CRCCTRL register:

• Swap byte in halfword

• Swap halfword

Input data width is 4 bytes, thus the configuration only affects the 4-byte word. The ENDIAN bit field

supports the configurations listed in Table 20-1, assuming the input word is {B3, B2, B1, B0}.

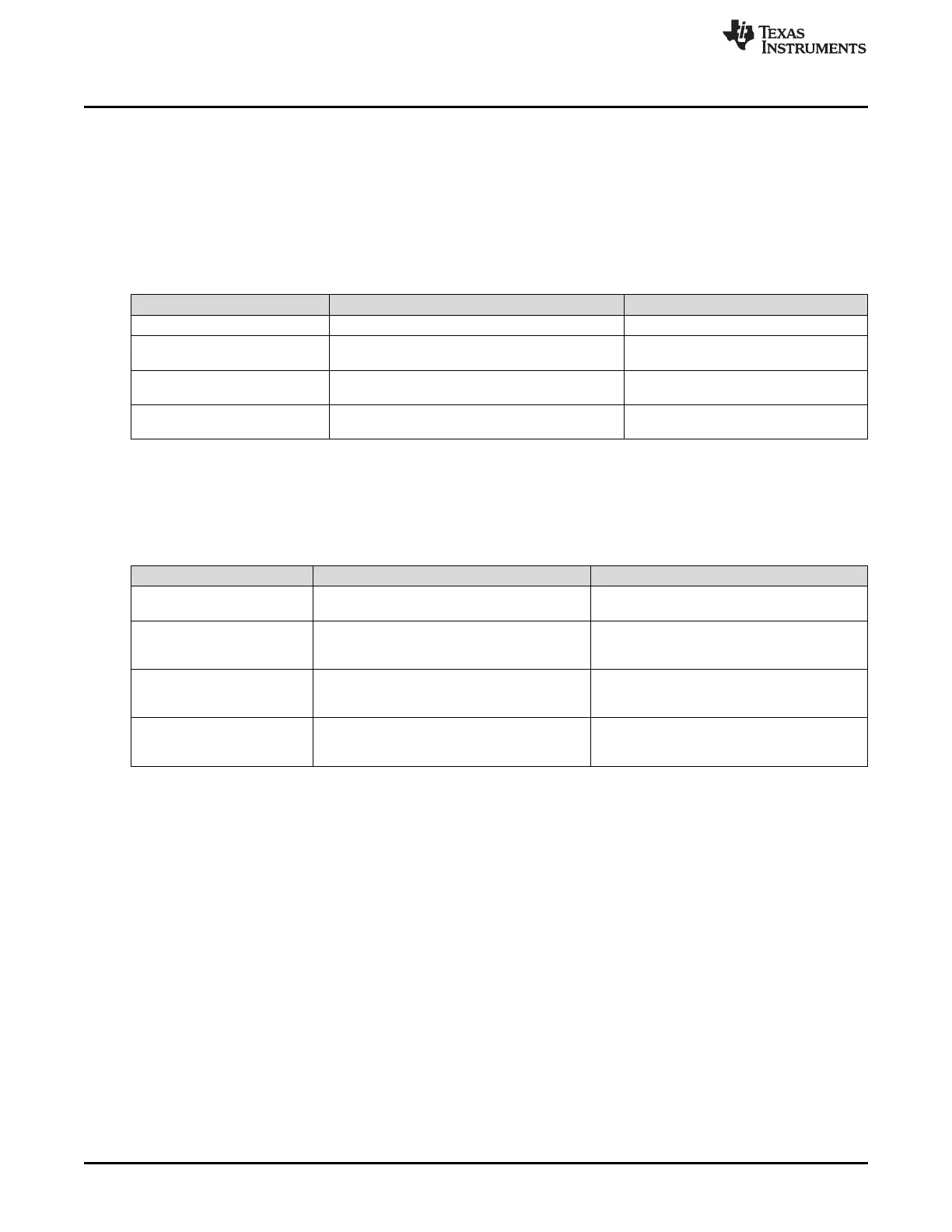

Table 20-1. Endian Configuration

ENDIAN Encoding Definition Configuration

0x0 Configuration unchanged. {B3, B2, B1, B0}

0x1 Bytes are swapped in halfwords, but halfwords are

not swapped

{B2, B3, B0, B1}

0x2 Halfwords are swapped, but bytes are not swapped

in halfword.

{B1, B0, B3, B2}

0x3 Bytes are swapped in halfwords, and halfwords are

swapped.

{B0, B1, B2, B3}

Bit reversal is supported by the BR bit in the CRCCTRL register. The bit reversal operation works in

tandem with endian control. For example, Table 20-1 with the BR option set would look like Table 20-2.

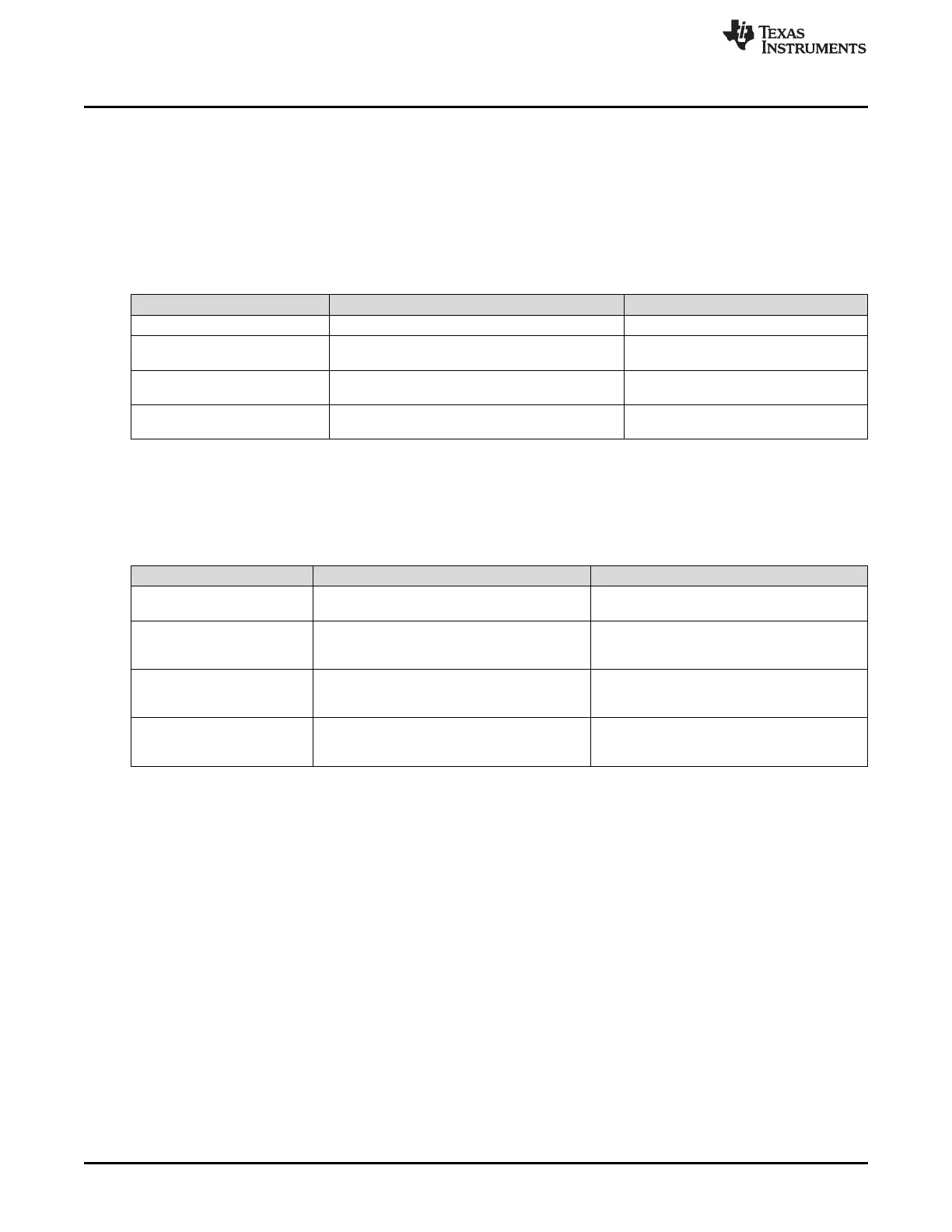

Table 20-2. Endian Configuration With Bit Reversal

ENDIAN Encoding Initial Endian Configuration Configuration With Bit Reversal (BR = 1)

0x0 Configuration unchanged

{B3[31:24], B2[23:16] , B1[15:8], B0[7:0]}

B3[24:31],B2[16:23],B1[8:15],B0[0:7]

0x1 Bytes are swapped in halfwords but halfwords

are not swapped.

{B2[23:16], B3[31:24], B0[7:0], B1[15:8]}

B2[16:23],B3[24:31],B0[0:7],B1[8:15]

0x2 Halfwords are swapped but bytes are not

swapped in halfword.

{B1[15:8], B0[7:0], B3[31:24], B2[23:16]}

B1[8:15],B0[0:7],B3[24:31],B2[16:23]

0x3 Bytes are swapped in halfwords and halfwords

are swapped.

{B0[7:0], B1[15:8], B2[23:16], B3[31:24]}

B0[0:7],B1[8:15],B2[16:23],B3[24:31]

Loading...

Loading...