SHA/MD5 Functional Description

www.ti.com

700

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

SHA/MD5 Accelerator

If the three passes are not performed in succession, the digest registers must be saved and restored for

the next use of the SHA/MD5 engine. If the rounds are performed consecutively, there is no need to do

anything with the digest registers.

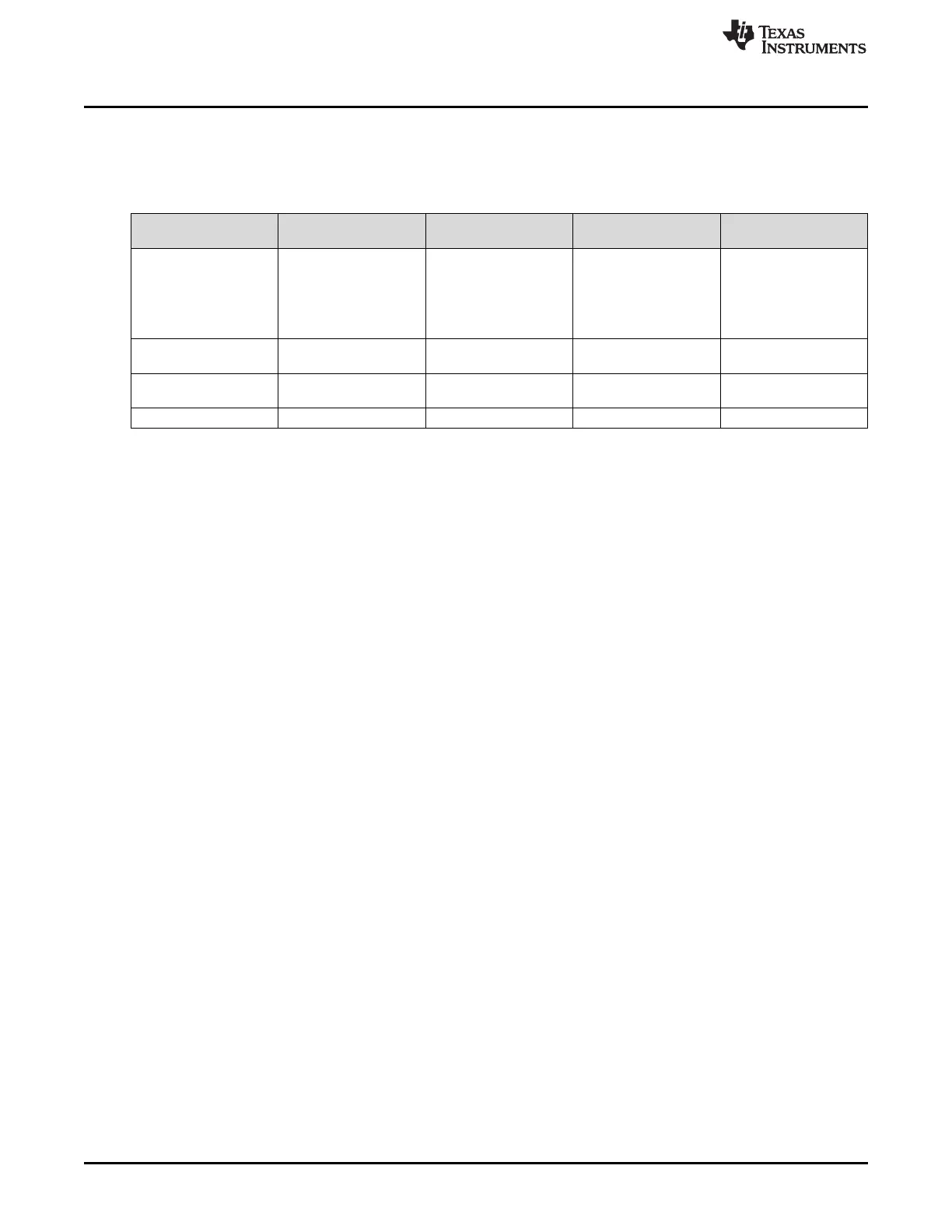

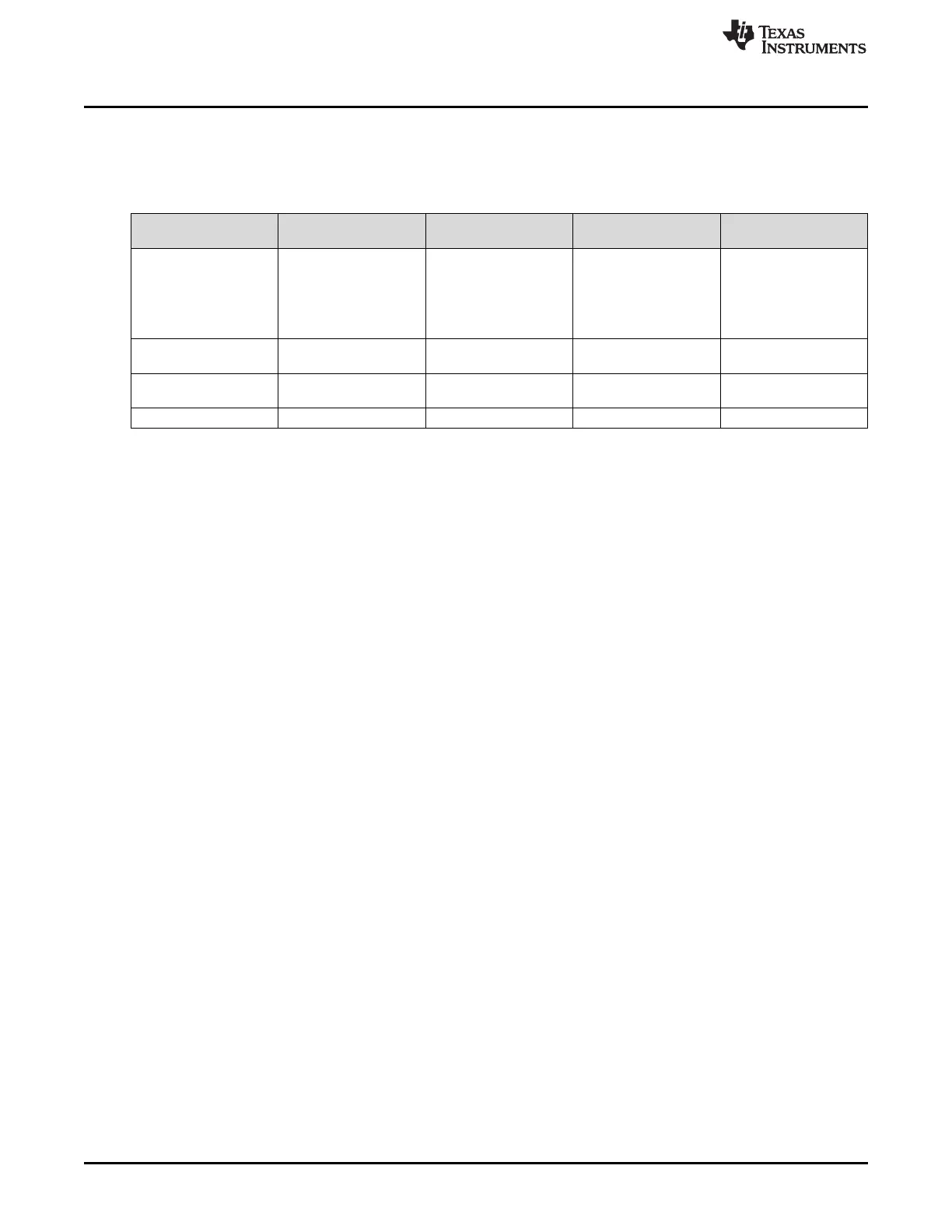

Table 19-6. SHA Digest Processed in One Pass

Digest (A to E) SHAMD5_DIGEST_CO

UNT

SHAMD5_MODE and

SHAMD5_LENGTH

SHAMD5_DATA_n_IN

First pass WRITE:

LENGTH=129

ALGO (dependent on

the algorithm to apply)

ALGO_CONSTANT=1

CLOSE_HASH=1

First 64 bytes of

message

Round 1 digest

calculation

Second 64 bytes of

message

Round 2 digest

calculation

Last byte of message

Final digest Read: 129

19.1.3.2 MD5 Mode

19.1.3.2.1 Starting a New Hash

To start a new hash, perform the following steps:

1. Set the ALGO bit field in the SHAMD5_MODE register to 0x0 to select the MD5 algorithm.

2. Set the ALGO_CONSTANT bit to 1 in the SHAMD5_MODE register to initialize all digest registers from

SHAMD5_ODIGEST_A/SHAMD5_IDIGEST_A to SHAMD5_ODIGEST_H/SHAMD5_IDIGEST_H with

default values specified by the algorithm, and set the SHAMD5_DIGESTCOUNT register to 0.

3. Specify the LENGTH field in the SHAMD5_LENGTH register of the hash data to process in bytes.

4. Set the CLOSE_HASH bit in the SHAMD5_MODE register to let the SHA/MD5 engine do the padding.

If MD5 is computed in one shot, the length of the message can be any value up to ? what?. To

process an intermediate MD5 digest, the CLOSE_HASH bit is set to 0, in which case packets to be

hashed must be 64 bytes; the last packet must be hashed with the CLOSE_HASH bit set to 1.

After the configuration is complete, the hash engine can receive the data to process (the INPUT_READY

bit is 1 in the SHAMD5_IRQSTATUS register). Data must be written to the 16 × 32-bit

SHAMD5_DATA_n_IN registers that provide storage for one 64-byte block of data. Unless the

CLOSE_HASH bit is set in the SHAMD5_MODE register, the SHAMD5_DATA_n_IN 64-byte input buffer

must be filled. Data can be written by single write transactions to the 16 registers from a processor or by a

µDMA transfer.

For a µDMA transfer, the SDAM_EN bit must be set in the SHAMD5_SYSCONFIG register before starting

the new hash and the µDMA channel for SHA/MD5 0 data in request must be configured. The µDMA must

be configured to the appropriate hash transfer size. A µDMA done is asserted after the last

SHAMD5_DATA_n_IN register is filled.

The module detects that a 64-byte block is available, and then moves the data to a working register space

for processing and sets the INPUT_READY bit to 1 in the SHAMD5_IRQSTATUS register. If the

PDMA_EN bit is set in the SHAMD5_SYSCONFIG register, then a new µDMA request triggers a new

block transfer; otherwise, the processor polls the INPUT_READY bit in the SHAMD5_IRQSTATUS register

and writes the 16 data words of 32 bits when it equals 1.

This operation repeats until the length of the message to hash is reached. The OUTPUT_READY bit in the

SHAMD5_IRQSTATUS register then indicates that the hash operation is complete. If the PIT_EN bit in the

SHAMD5_SYSCONFIG register is set, an interrupt (active low) is also generated to indicate the hash

completion.

Loading...

Loading...