I2S Registers

www.ti.com

438

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

Inter-Integrated Sound (I2S) Multichannel Audio Serial Port

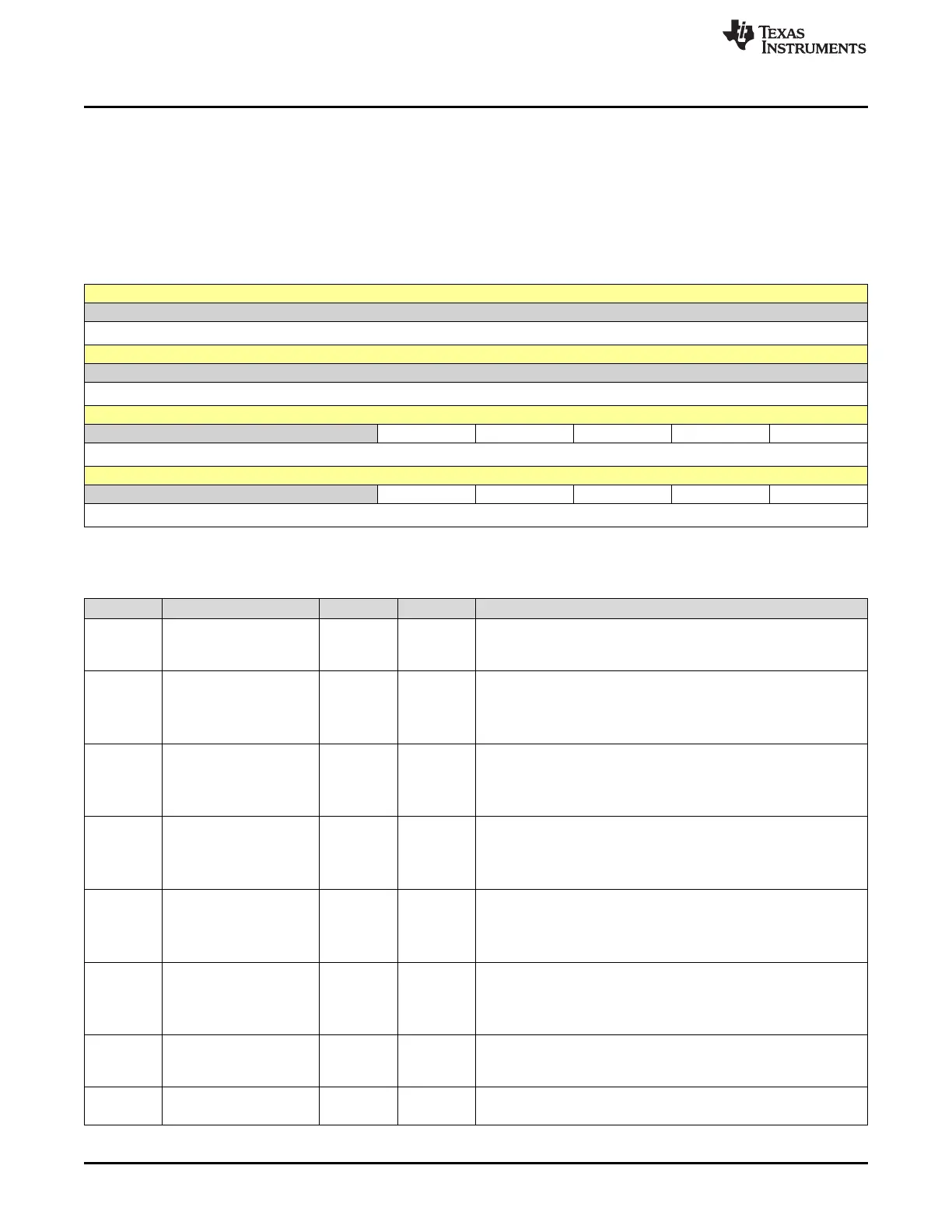

12.5.16 XGBLCTL Register (Offset = A0h) [reset = 0h]

XGBLCTL is shown in Figure 12-19 and described in Table 12-21.

Return to Summary Table.

Alias of the global control register (GBLCTL). Writing to the transmitter global control register (XGBLCTL)

affects only the transmit bits of GBLCTL (bits 12-8). Reads from XGBLCTL return the value of GBLCTL.

XGBLCTL allows the transmitter to be reset independently from the receiver.

Figure 12-19. XGBLCTL Register

31 30 29 28 27 26 25 24

RESERVED

R-0h

23 22 21 20 19 18 17 16

RESERVED

R-0h

15 14 13 12 11 10 9 8

RESERVED XFRST XSMRST XSRCLR XHCLKRST XCLKRST

R-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h

7 6 5 4 3 2 1 0

RESERVED RFRST RSMRST RSRCLR RHCLKRST RCLKRST

R-0h R-0h R-0h R-0h R-0h R-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

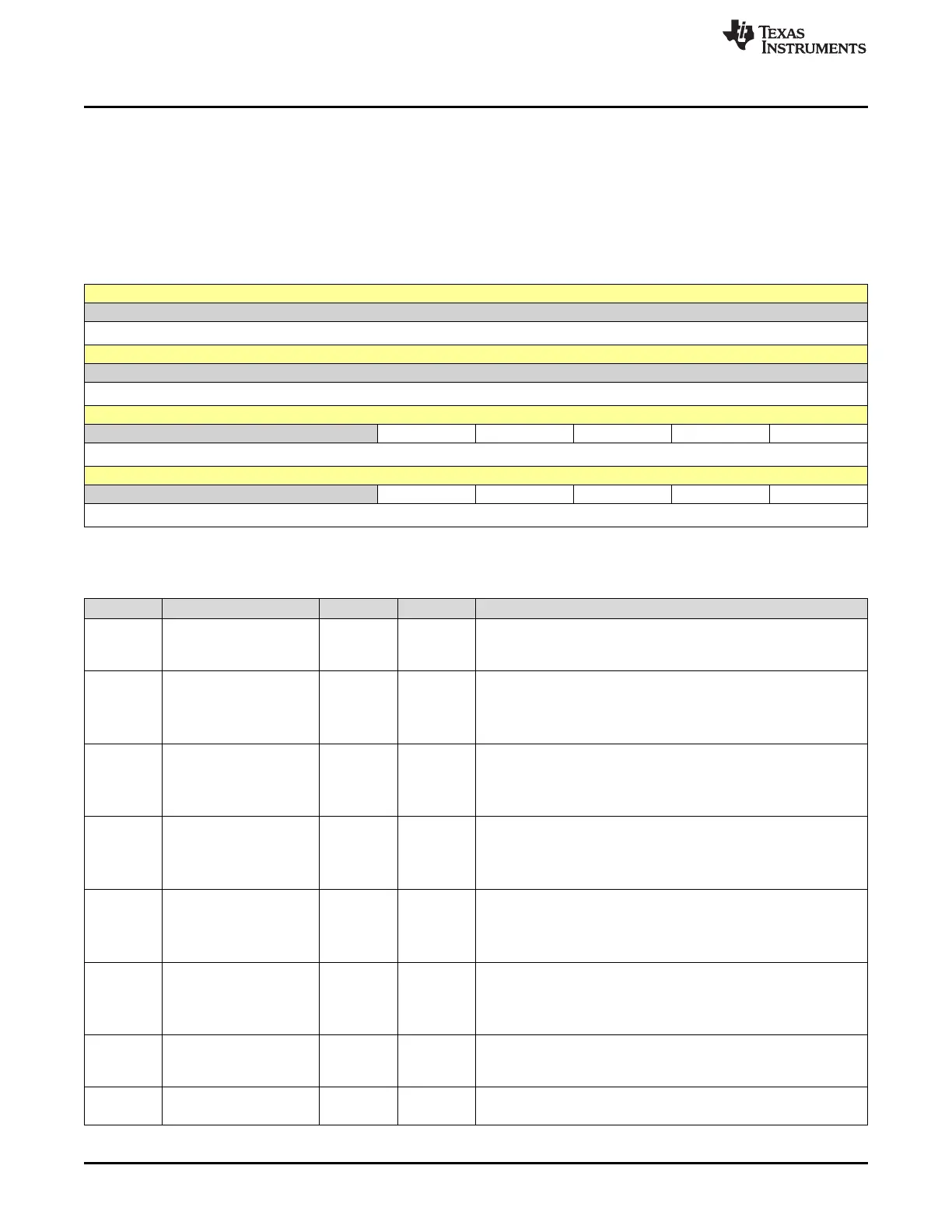

Table 12-21. XGBLCTL Register Field Descriptions

Bit Field Type Reset Description

31-13 RESERVED R 0h

Reserved. The reserved bit location always returns the default value.

A value written to this field has no effect. If writing to this field,

always write the default value for future device compatibility.

12 XFRST R/W 0h

Transmit frame sync generator reset enable bit. A write to this bit

affects the XFRST bit of GBLCTL.

0h = Transmit frame sync generator is reset.

1h = Transmit frame sync generator is active.

11 XSMRST R/W 0h

Transmit state machine reset enable bit. A write to this bit affects the

XSMRST bit of GBLCTL.

0h = Transmit state machine is held in reset.

1h = Transmit state machine is released from reset.

10 XSRCLR R/W 0h

Transmit serializer clear enable bit. A write to this bit affects the

XSRCLR bit of GBLCTL.

0h = Transmit serializers are cleared.

1h = Transmit serializers are active.

9 XHCLKRST R/W 0h

Transmit high-frequency clock divider reset enable bit. A write to this

bit affects the XHCLKRST bit of GBLCTL.

0h = Transmit high-frequency clock divider is held in reset.

1h = Transmit high-frequency clock divider is running.

8 XCLKRST R/W 0h

Transmit clock divider reset enable bit. A write to this bit affects the

XCLKRST bit of GBLCTL.

0h = Transmit clock divider is held in reset.

1h = Transmit clock divider is running.

7-5 RESERVED R 0h

Reserved. The reserved bit location always returns the default value.

A value written to this field has no effect. If writing to this field,

always write the default value for future device compatibility.

4 RFRST R 0h

Receive frame sync generator reset enable bit. A read of this bit

returns the RFRST bit value of GBLCTL. Writes have no effect.

Loading...

Loading...