www.ti.com

SHA/MD5 Functional Description

703

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

SHA/MD5 Accelerator

19.1.4.1.5 Operational Modes Configuration

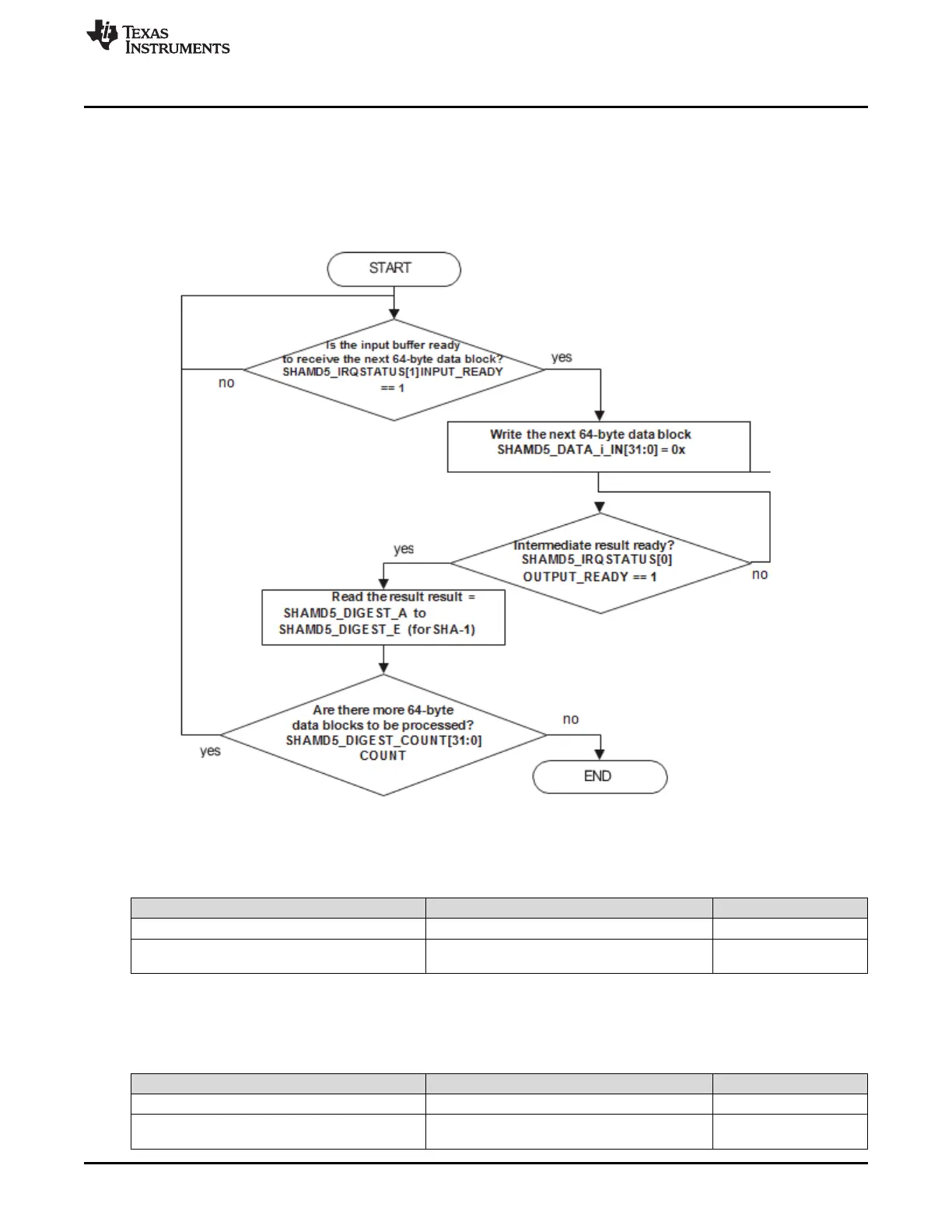

SHA/MD5 polling mode: Figure 19-2 shows the SHA/MD5 polling mode. SHA/MD5 polling mode uses the

following registers: SHAMD5_IRQSTATUS, SHAMD5_DATA_n_IN, SHAMD5_ODIGEST_A,

SHAMD5_DIGEST_COUNT, and SHAMD5_LENGTH.

Figure 19-2. SHA/MD5 Polling Mode

SHA/MD5 interrupt mode: the procedure in Table 19-9 configures the SHA/MD5 module to work in

interrupt-based mode. (For the interrupt subroutine, see Section 19.1.4.1.6.1.)

Table 19-9. Interrupt Mode

Step Register/Bit Field/Programming Model Value

Enable the interrupt request to the processor. SHAMD5_SYSCONFIG[2] P IT_EN 0x1

Load the message length; this is the trigger to start

processing.

SHAMD5_LENGTH[31:0] LENGTH –

SHA/MD5 DMA mode: the procedure in Table 19-10 configures the SHA/MD5 module to work in DMA-

based mode.

Table 19-10. DMA Mode

Step Register/Bit Field/Programming Model Value

Enable the DMA request to the CDMA controller. SHAMD5_SYSCONFIG[3] P DMA_EN 0x1

Load the message length; this is the trigger to start

processing.

SHAMD5_LENGTH[31:0] LENGTH –

Loading...

Loading...