SD-HOST Registers

www.ti.com

394

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

SD Host Controller Interface

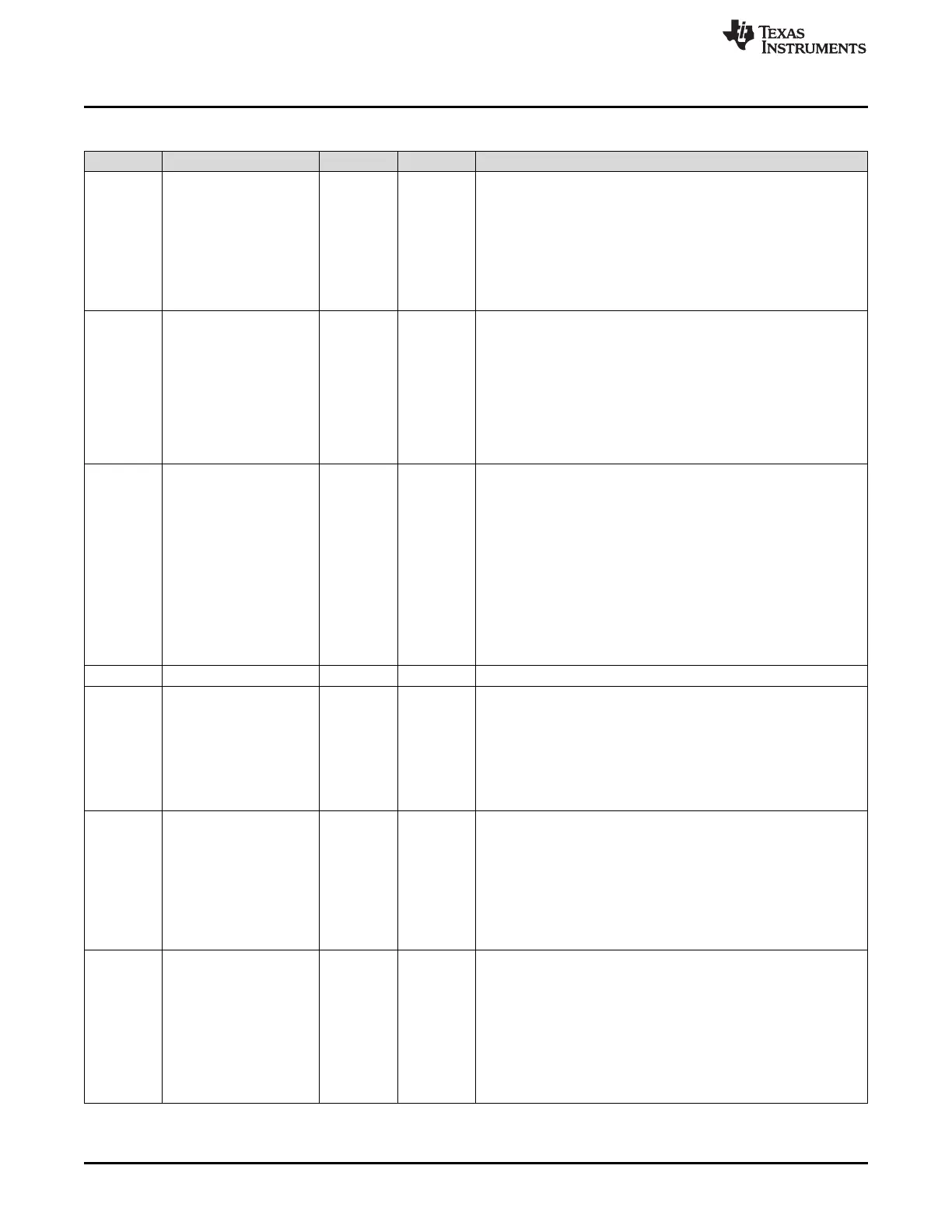

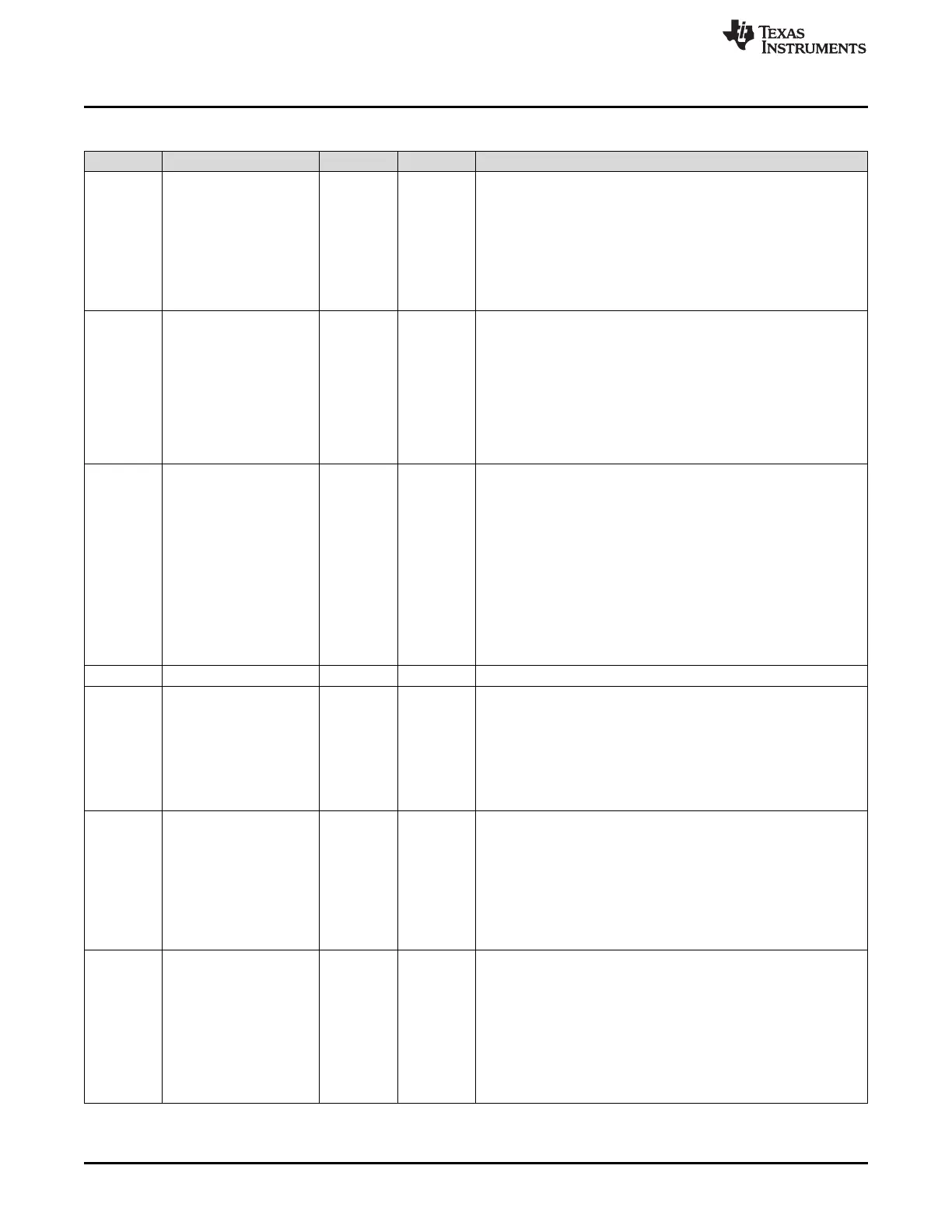

Table 11-18. MMCHS_STAT Register Field Descriptions (continued)

Bit Field Type Reset Description

22 DEB R/W 0h

Data End Bit error

This bit is set automatically when detecting a 0 at the end bit position

of read data on mmci_dat line, or at the end position of the CRC

status in write mode.

Read 0h = No error

Write 0h = Status bit unchanged

Read 1h = Data end bit error

Write 1h = Status is cleared

21 DCRC R/W 0h

Data CRC error

This bit is set automatically when there is a CRC16 error in the data

phase response following a block read command, or if there is a 3-

bit CRC status different of a position 010 token during a block write

command.

Read 0h = No error

Write 0h = Status bit unchanged

Read 1h = Data CRC error

Write 1h = Status is cleared

20 DTO R/W 0h

Data time-out error

This bit is set automatically according to the following conditions:

• Busy time-out for R1b, R5b response type

• Busy time-out after write CRC status

• Write CRC status time-out

• Read data time-out

Read 0h = No error

Write 0h = Status bit unchanged

Read 1h = Time-out

Write 1h = Status is cleared

19 RESERVED R 0h

18 CEB R/W 0h

Command end bit error

This bit is set automatically when detecting a 0 at the end bit position

of a command response.

Read 0h = No error

Write 0h = Status bit unchanged

Read 1h = Command end bit error

Write 1h = Status is cleared

17 CCRC R/W 0h

Command CRC error

This bit is set automatically when there is a CRC7 error in the

command response, depending on the enable bit

(MMCi.MMCHS_CMD[19] CCCE).

Read 0h = No error

Write 0h = Status bit unchanged

Read 1h = Command CRC error

Write 1h = Status is cleared

16 CTO R/W 0h

Command time-out error

This bit is set automatically when no response is received within 64

clock cycles from the end bit of the command. For commands that

reply within 5 clock cycles, the time-out is still detected at 64 clock

cycles.

Read 0h = No error

Write 0h = Status bit unchanged

Read 1h = Time-out

Write 1h = Status is cleared

Loading...

Loading...