Functional Description

www.ti.com

310

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

General-Purpose Timers

If software updates the GPTMTnILR or the GPTMTnPR register while the counter is counting down, the

counter loads the new value on the next clock cycle and continues counting from the new value if the

TnILD bit in the GPTMTnMR register is clear. If the TnILD bit is set, the counter loads the new value after

the next time-out. If software updates the GPTMTnILR or the GPTMTnPR register while the counter is

counting up, the time-out event is changed on the next cycle to the new value. If software updates the

GPTM Timer n Value (GPTMTnV) register while the counter is counting up or down, the counter loads the

new value on the next clock cycle and continues counting from the new value. If software updates the

GPTMTnMATCHR or the GPTMTnPMR registers, the new values are reflected on the next clock cycle if

the TnMRSU bit in the GPTMTnMR register is clear. If the TnMRSU bit is set, the new value does not take

effect until the next time-out.

If the TnSTALL bit in the GPTMCTL register is set, the timer freezes counting while the debugger halts the

processor. The timer resumes counting when the processor resumes execution.

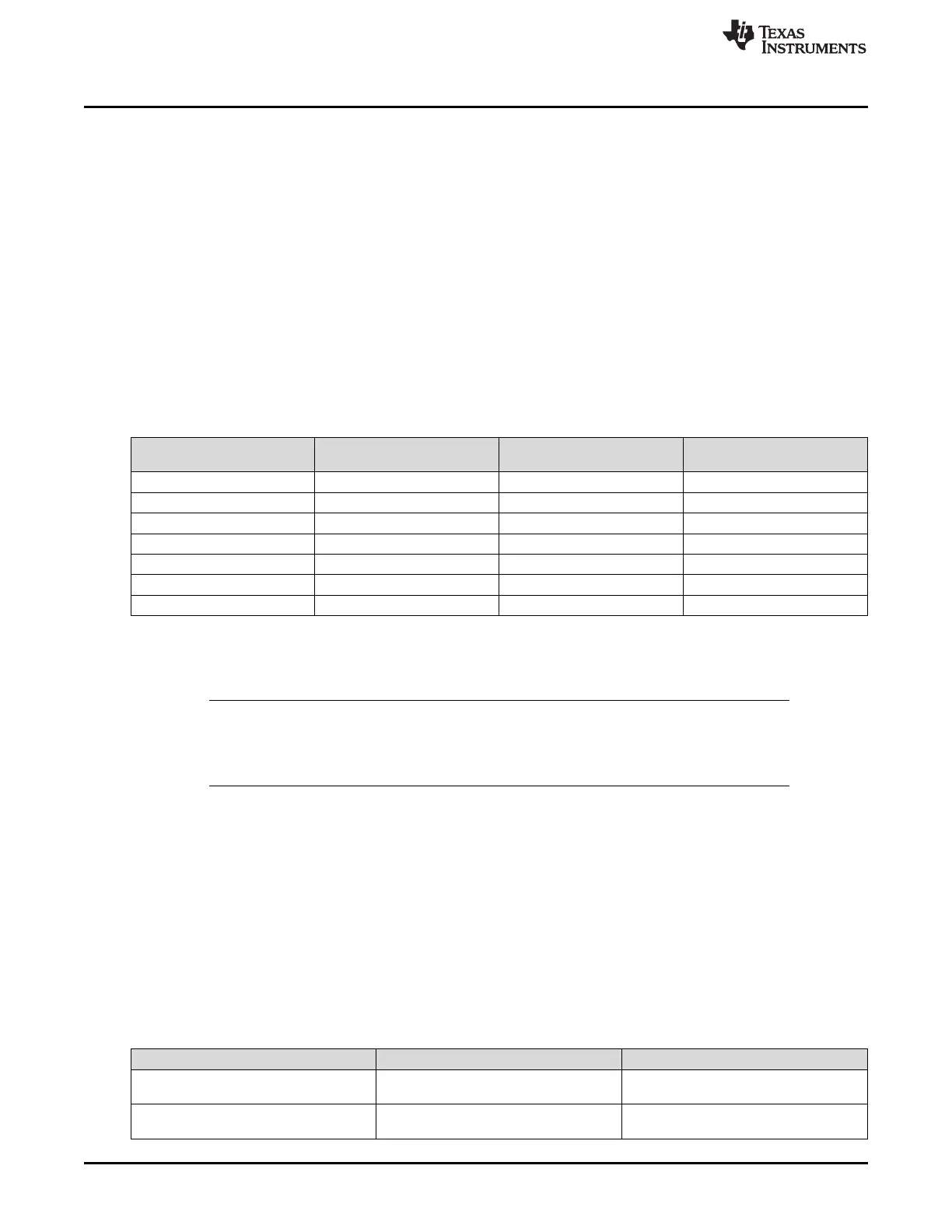

Table 9-4 lists a variety of configurations for a 16-bit free-running timer while using the prescaler. All

values assume an 80-MHz clock with Tc = 12.5 ns (clock period). The prescaler can only be used when a

16/32-bit timer is configured in 16-bit mode.

(1)

Tc is the clock period.

Table 9-4. 16-Bit Timer With Prescaler Configurations

Prescale (8-Bit Value)

Number of Timer Clocks

(Tc)

(1)

Maximum Time Units

00000000 1 0.8192 ms

00000001 2 1.6384 ms

00000010 3 2.4576 ms

– – – –

11111101 254 208.0768 ms

11111110 255 208.896 ms

11111111 256 209.7152 ms

9.3.2.2 Input Edge-Count Mode

NOTE: For rising-edge detection, the input signal must be high for at least two clock periods

following the rising edge. Similarly, for falling-edge detection, the input signal must be low for

at least two clock periods following the falling edge. Based on this criteria, the maximum

input frequency for edge detection is 1/4 of the frequency.

In edge-count mode, the timer is configured as a 24-bit up counter or down counter, including the optional

prescaler with the upper count value stored in the GPTM Timer n Prescale (GPTMTnPR) register and the

lower bits in the GPTMTnR register. In this mode, the timer can capture three types of events: rising edge,

falling edge, or both. To place the timer in edge-count mode, the TnCMR bit of the GPTMTnMR register

must be cleared. The type of edge that the timer counts is determined by the TnEVENT fields of the

GPTMCTL register. During initialization in down-count mode, the GPTMTnMATCHR and GPTMTnPMR

registers are configured so that the difference between the value in the GPTMTnILR and GPTMTnPR

registers and the GPTMTnMATCHR and GPTMTnPMR registers equals the number of edge events that

must be counted. In up-count mode, the timer counts from 0x0 to the value in the GPTMTnMATCHR and

GPTMTnPMR registers. When executing an up-count, the value of GPTMTnPR and GPTMTnILR must be

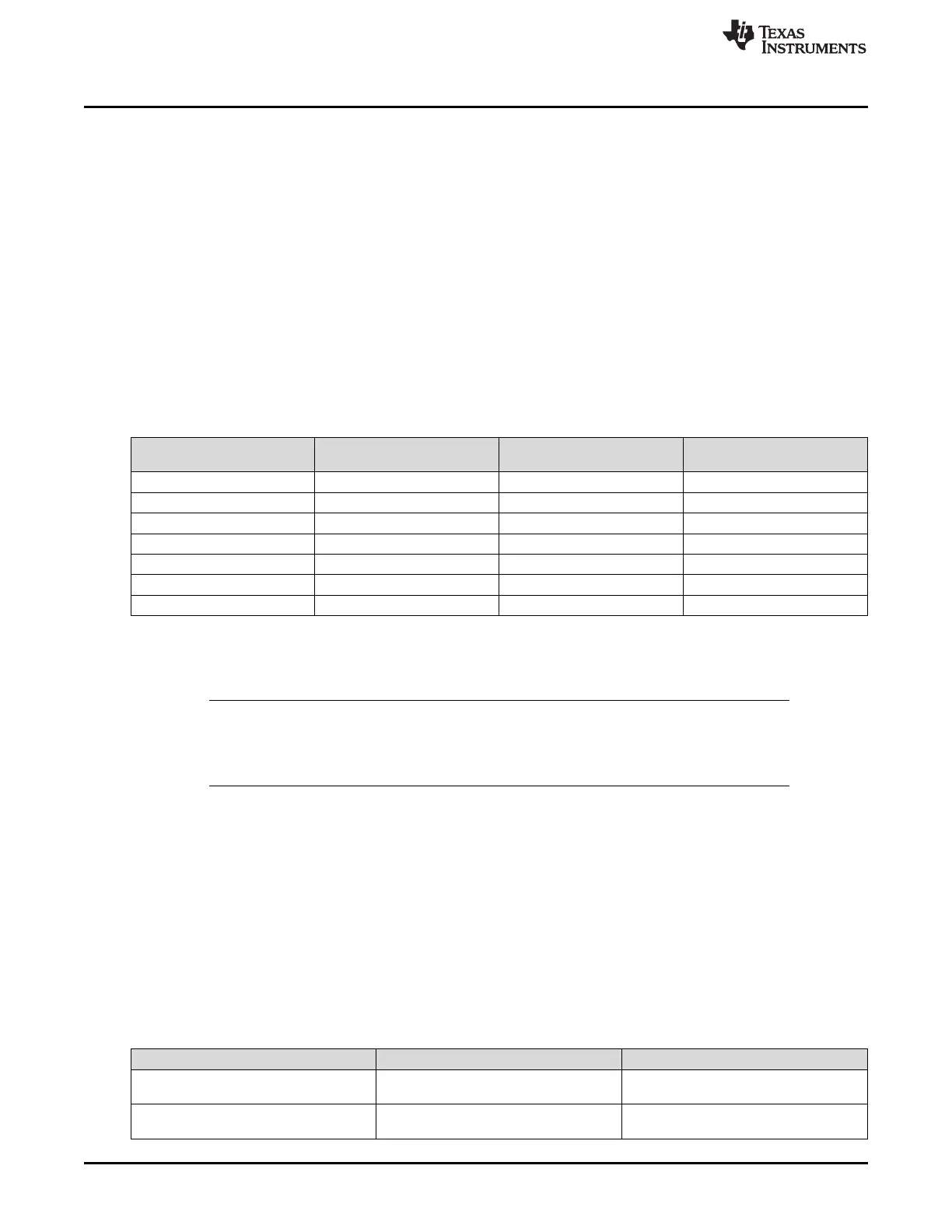

greater than the value of GPTMTnPMR and GPTMTnMATCHR. Table 9-5 lists the values loaded into the

timer registers when the timer is enabled.

Table 9-5. Counter Values When the Timer is Enabled in Input Edge-Count Mode

Register Count-Down Mode Count-Up Mode

GPTMTnR

GPTMTnPR in combination with

GPTMTnILR

0x0

GPTMTnV

GPTMTnPR in combination with

GPTMTnILR

0x0

Loading...

Loading...