www.ti.com

Register Map

111

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

Cortex

®

-M4 Peripherals

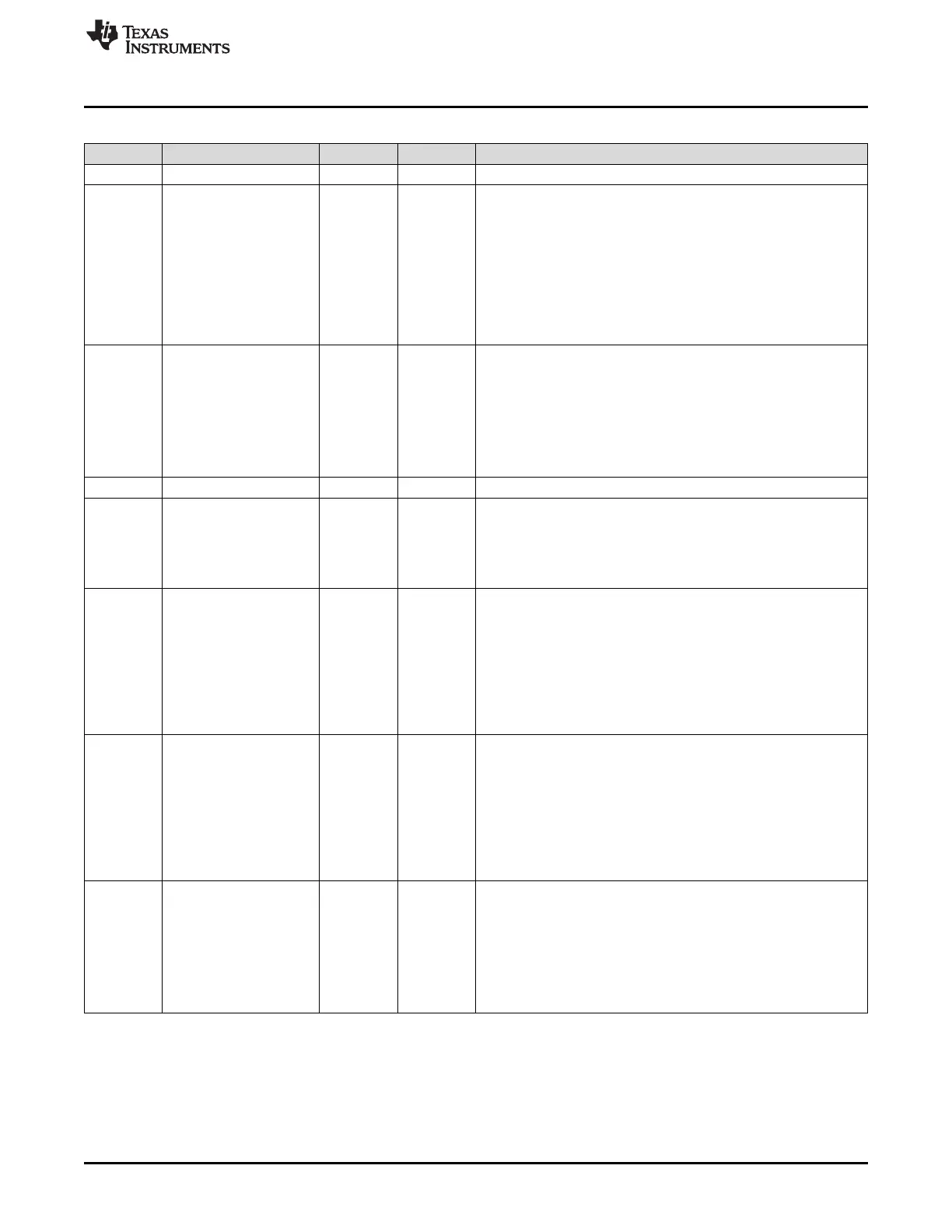

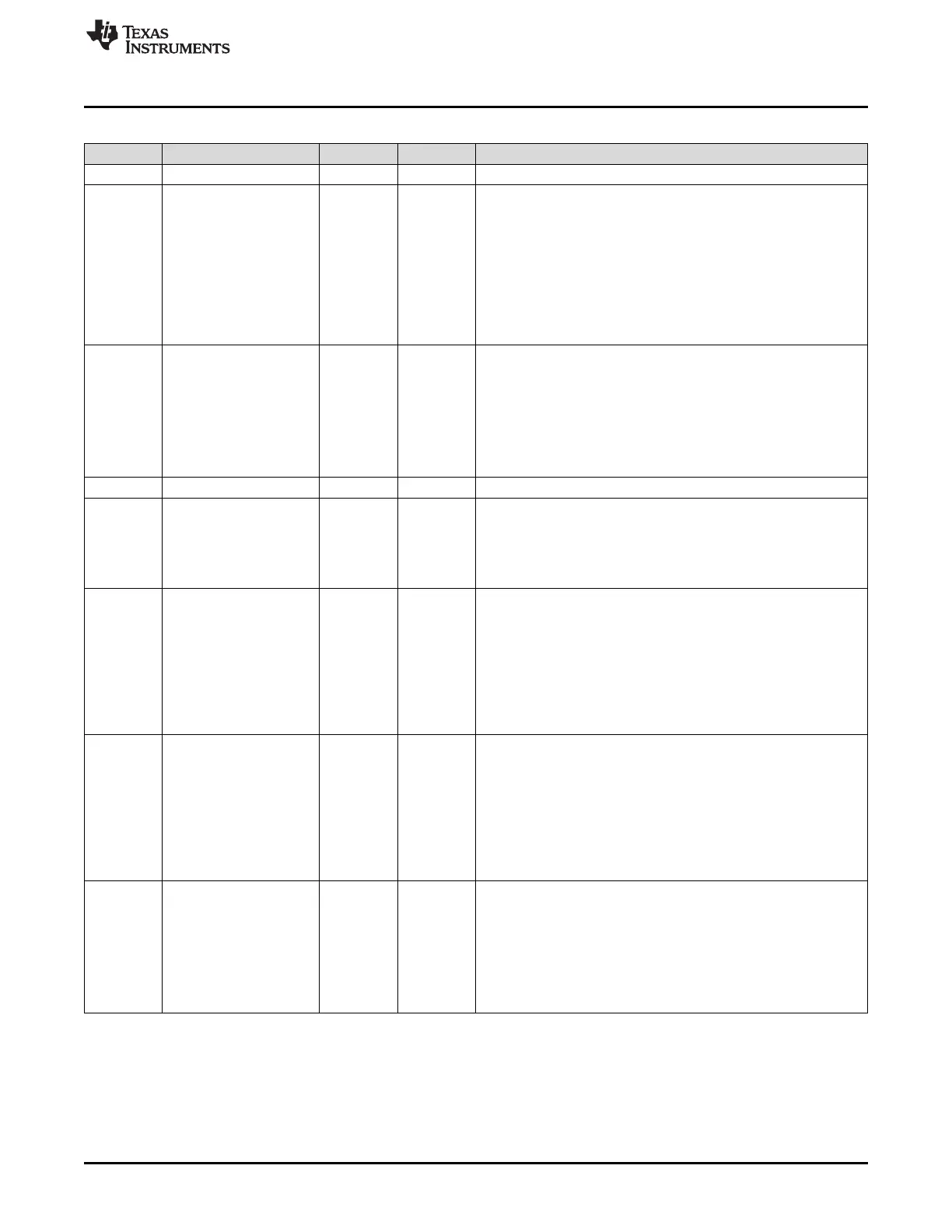

Table 3-24. FAULTSTAT Register Field Descriptions

Bit Field Type Reset Description

31-26 RESERVED R 0h

25 DIV0 R/W1C 0h

Divide-by-Zero Usage Fault

When this bit is set, the PC value stacked for the exception return

points to the instruction that performed the divide by zero. Trapping

on divide-by-zero is enabled by setting the DIV0 bit in the

Configuration and Control (CFGCTRL) register. This bit is cleared by

writing a 1 to it.

0h = No divide-by-zero fault has occurred, or divide-by-zero trapping

is not enabled.

1h = The processor has executed an SDIV or UDIV instruction with a

divisor of 0.

24 UNALIGN R/W1C 0h

Unaligned Access Usage Fault

Unaligned LDM, STM, LDRD, and STRD instructions always fault

regardless of the configuration of this bit. Trapping on unaligned

access is enabled by setting the UNALIGNED bit in the CFGCTRL

register. This bit is cleared by writing a 1 to it.

0h = No unaligned access fault has occurred, or unaligned access

trapping is not enabled.

1h = The processor has made an unaligned memory access.

23-20 RESERVED R 0h

19 NOCP R/W1C 0h

No Coprocessor Usage Fault

This bit is cleared by writing a 1 to it.

0h = A usage fault has not been caused by attempting to access a

coprocessor.

1h = The processor has attempted to access a coprocessor.

18 INVPC R/W1C 0h

Invalid PC Load Usage Fault

When this bit is set, the PC value stacked for the exception return

points to the instruction that tried to perform the illegal load of the

PC. This bit is cleared by writing a 1 to it.

0h = A usage fault has not been caused by attempting to load an

invalid PC value.

1h = The processor has attempted an illegal load of EXC_RETURN

to the PC as a result of an invalid context or an invalid

EXC_RETURN value.

17 INVSTAT R/W1C 0h

Invalid State Usage Fault

When this bit is set, the PC value stacked for the exception return

points to the instruction that attempted the illegal use of the

Execution Program Status Register (EPSR) register. This bit is not

set if an undefined instruction uses the EPSR register. This bit is

cleared by writing a 1 to it.

0h = A usage fault has not been caused by an invalid state.

1h = The processor has attempted to execute an instruction that

makes illegal use of the EPSR register.

16 UNDEF R/W1C 0h

Undefined Instruction Usage Fault

When this bit is set, the PC value stacked for the exception return

points to the undefined instruction. An undefined instruction is an

instruction that the processor cannot decode. This bit is cleared by

writing a 1 to it.

0h = A usage fault has not been caused by an undefined instruction.

1h = The processor has attempted to execute an undefined

instruction.

Loading...

Loading...