www.ti.com

UART Registers

185

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

Universal Asynchronous Receivers/Transmitters (UARTs)

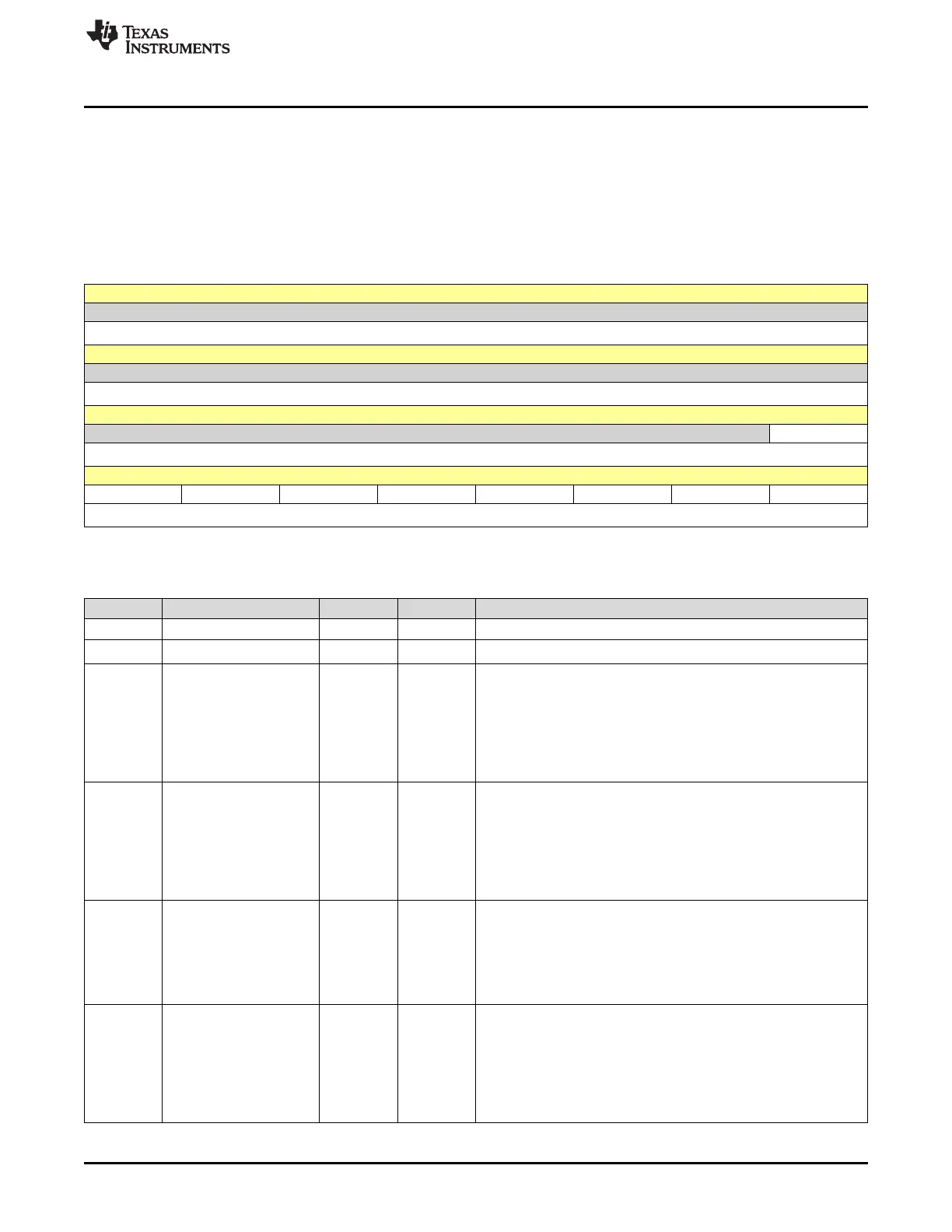

6.3.3 UARTFR Register (Offset = 18h) [reset = 90h]

UARTFR is shown in Figure 6-5 and described in Table 6-5.

Return to Summary Table.

The UARTFR register is the flag register. After reset, the TXFF, RXFF, and BUSY bits are 0, and TXFE

and RXFE bits are 1. The RI and CTS bits indicate the modem flow control and status. The modem bits

are only implemented on UART1 and are reserved on UART0.

Figure 6-5. UARTFR Register

31 30 29 28 27 26 25 24

RESERVED

R-0h

23 22 21 20 19 18 17 16

RESERVED

R-0h

15 14 13 12 11 10 9 8

RESERVED RI

R-0h R-0h

7 6 5 4 3 2 1 0

TXFE RXFF TXFF EXFE BUSY DCD DSR CTS

R-1h R-0h R-0h R-1h R-0h R-0h R-0h R-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

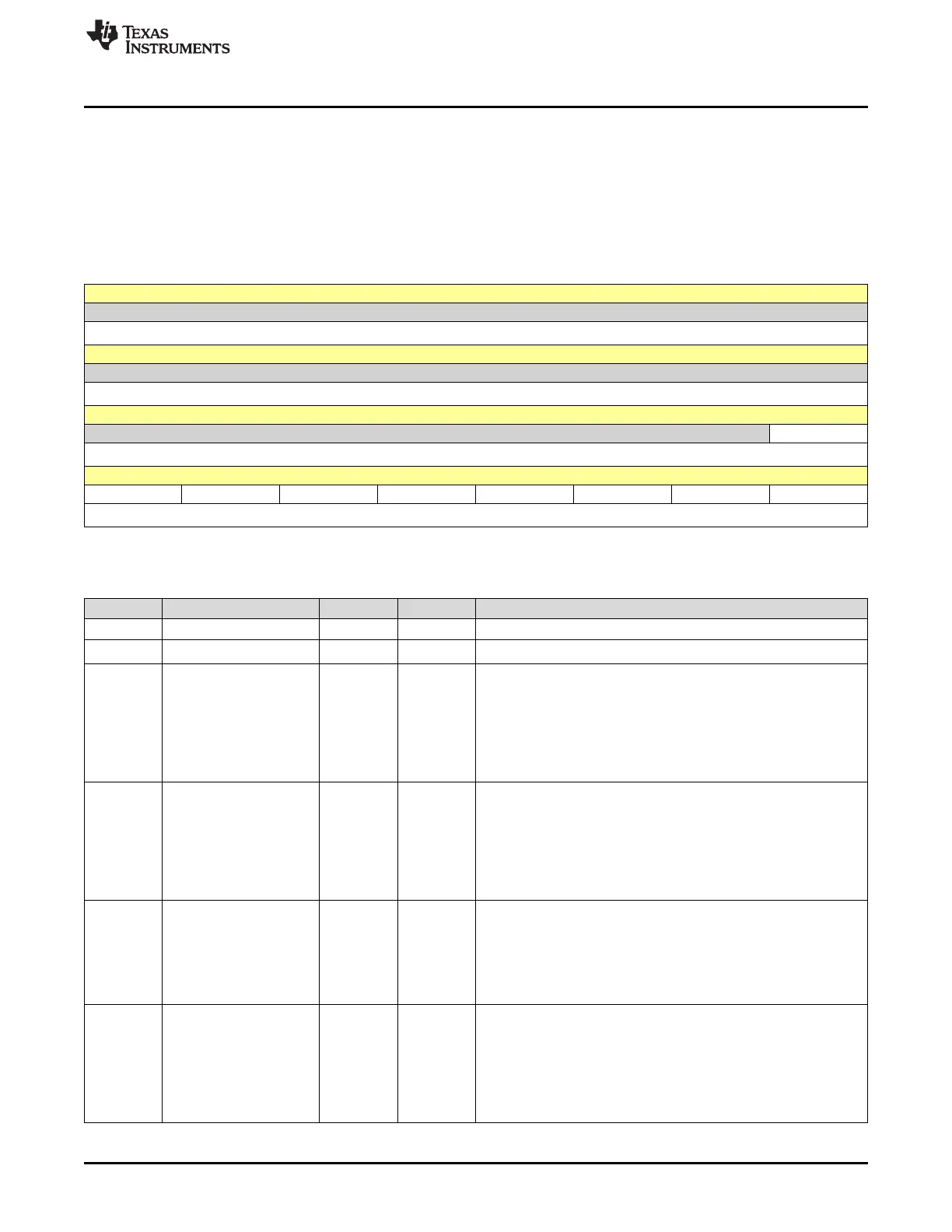

Table 6-5. UARTFR Register Field Descriptions

Bit Field Type Reset Description

31-9 RESERVED R 0h

8 RI R 0h

Reserved

7 TXFE R 1h

UART Transmit FIFO Empty

The meaning of this bit depends on the state of the FEN bit in the

UARTLCRH register. If the FIFO is enabled (FEN is 1), the transmit

FIFO is empty.

0h = The transmitter has data to transmit.

1h = If the FIFO is disabled (FEN is 0), the transmit holding register

is empty.

6 RXFF R 0h

UART Receive FIFO Full

The meaning of this bit depends on the state of the FEN bit in the

UARTLCRH register. If the FIFO is enabled (FEN is 1), the receive

FIFO is full.

0h = The receiver can receive data.

1h = If the FIFO is disabled (FEN is 0), the receive holding register is

full.

5 TXFF R 0h

UART Transmit FIFO Full

The meaning of this bit depends on the state of the FEN bit in the

UARTLCRH register.

0h = The transmitter is not full.

1h = If the FIFO is disabled (FEN is 0), the transmit holding register

is full. If the FIFO is enabled (FEN is 1), the transmit FIFO is full.

4 EXFE R 1h

UART Receive FIFO Empty

The meaning of this bit depends on the state of the FEN bit in the

UARTLCRH register. If the FIFO is enabled (FEN is 1), the receive

FIFO is empty.

0h = The receiver is not empty.

1h = If the FIFO is disabled (FEN is 0), the receive holding register is

empty.

Loading...

Loading...