www.ti.com

AES Registers

653

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

Advance Encryption Standard Accelerator (AES)

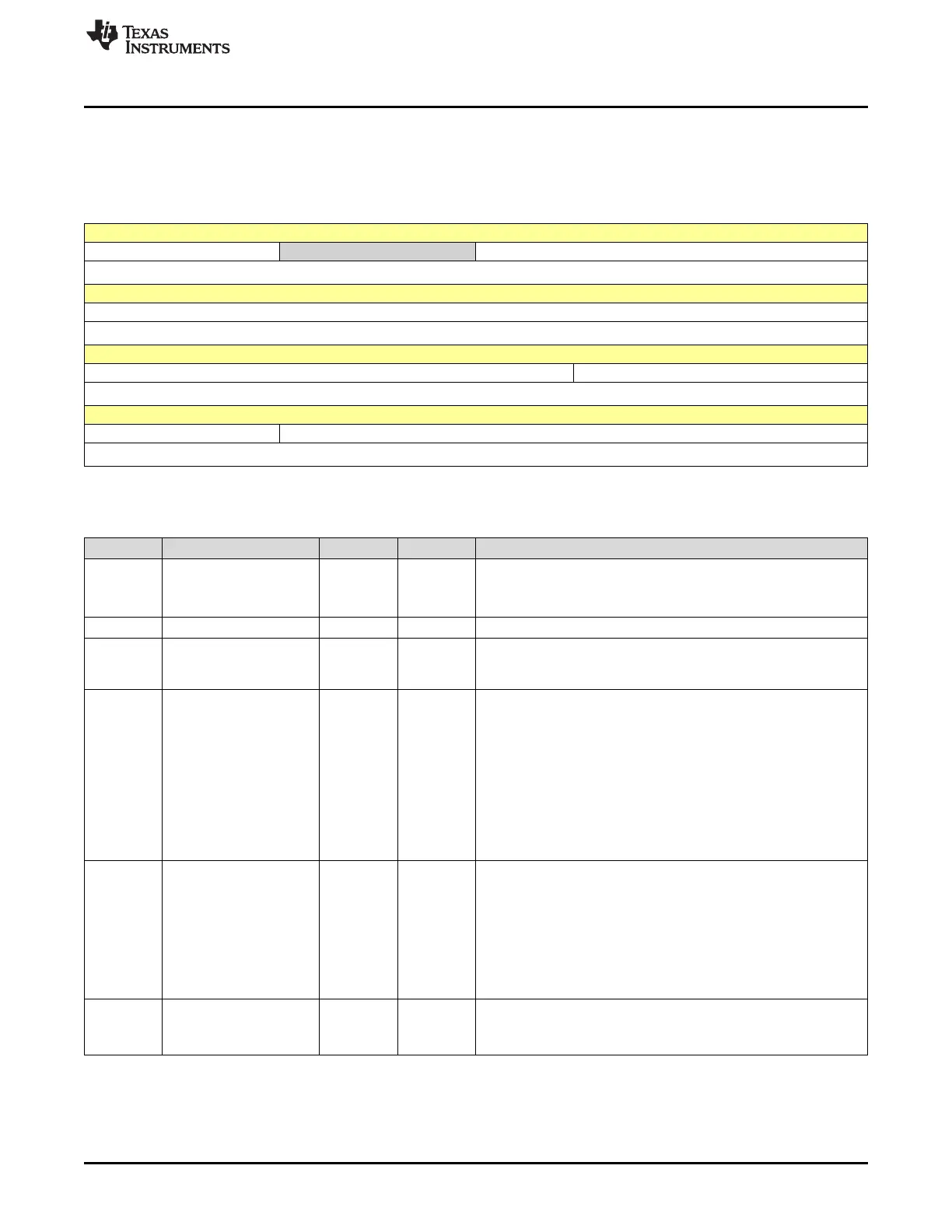

17.4.33 AES_REVISION Register (Offset = 80h) [reset = X]

AES_REVISION is shown in Figure 17-46 and described in Table 17-36.

Return to Summary Table.

Figure 17-46. AES_REVISION Register

31 30 29 28 27 26 25 24

SCHEME RESERVED FUNC

RO-0h R-X RO-0h

23 22 21 20 19 18 17 16

FUNC

RO-0h

15 14 13 12 11 10 9 8

R_RTL X_MAJOR

RO-0h RO-0h

7 6 5 4 3 2 1 0

CUSTOM Y_MINOR

RO-0h RO-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

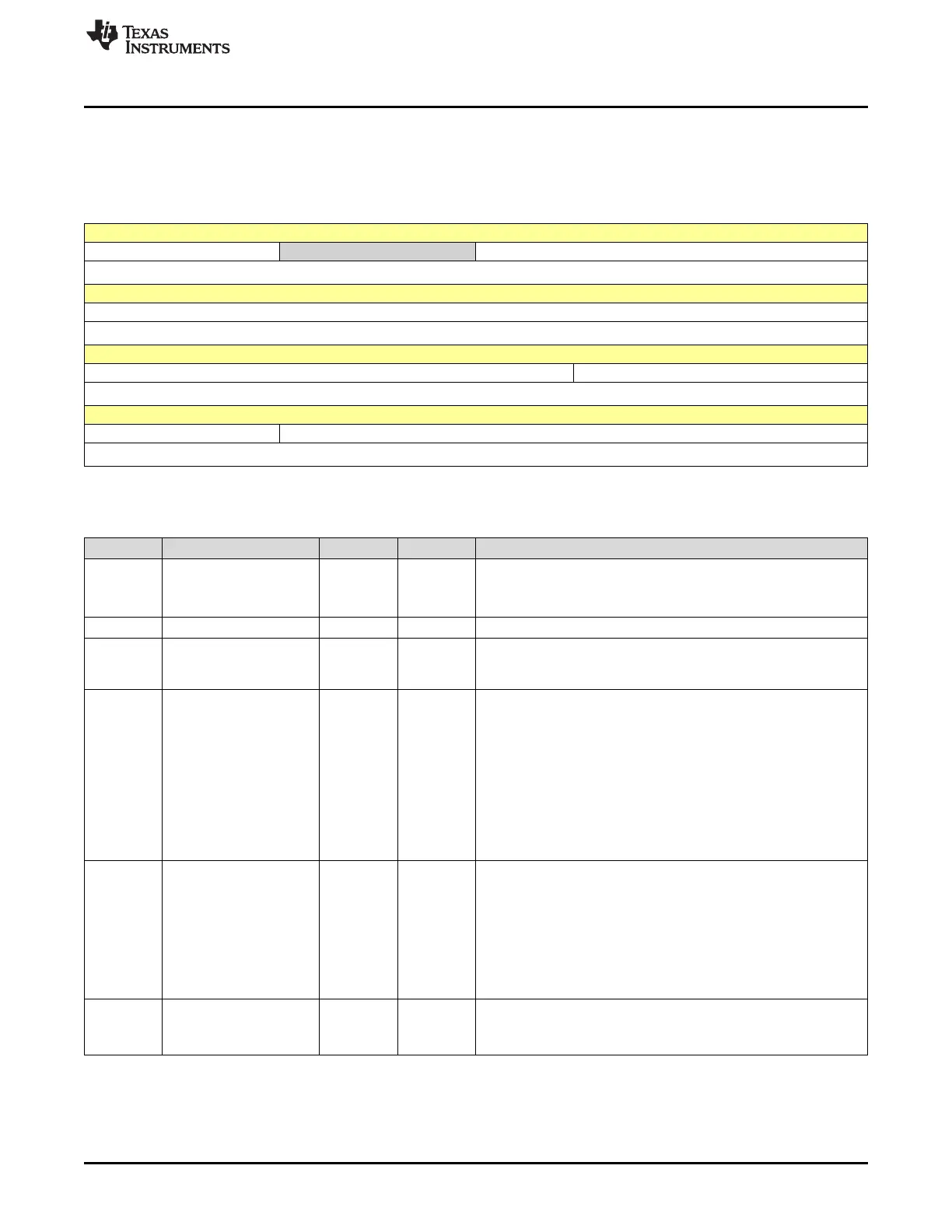

Table 17-36. AES_REVISION Register Field Descriptions

Bit Field Type Reset Description

31-30 SCHEME RO 0h

Used to distinguish between old scheme and current.

0h = (Read): Legacy ASP or WTBU scheme

1h = (Read): Highlander 0.8 scheme

29-28 RESERVED R X

27-16 FUNC RO 0h

Function indicates a software compatible module family. If there is

no level of software compatibility, a new Func number (and hence

REVISION) should be assigned.

15-11 R_RTL RO 0h

RTL Version (R), maintained by IP design owner.

RTL follows a numbering such as X.Y.R.Z which are explained in

this table.

R changes ONLY when:

(1) PDS uploads occur which may have been due to spec changes

(2) Bug fixes occur

(3) Resets to 0 when X or Y changes.

Design team has an internal Z (customer-invisible) number which

increments on every drop that happens due to DV and RTL updates.

Z resets to 0 when R increments.

10-8 X_MAJOR RO 0h

Major Revision (X), maintained by IP specification owner.

X changes ONLY when:

(1) There is a major feature addition. An example would be adding

master mode to Utopia Level2. The Func field (or class/type in old

PID format) remains the same.

X does NOT change due to:

(1) Bug fixes

(2) Change in feature parameters.

7-6 CUSTOM RO 0h

Indicates a special version for a particular device. Consequence of

use may avoid use of standard Chip Support Library (CSL) / Drivers.

0h = (Read): Non-custom (standard) revision

Loading...

Loading...