www.ti.com

Register Description

145

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

Direct Memory Access (DMA)

4.3.4.13 DMA_ALTSET Register (offset = 30h) [reset = 0h]

DMA_ALTSET is shown in Figure 4-19 and described in Table 4-23.

Each bit of this register represents the corresponding DMA channel. Setting a bit configures the DMA

channel to use the alternate control data structure. Reading the register returns the status of which control

data structure is in use for the corresponding DMA channel. For Ping-Pong and Scatter-Gather cycle

types, the DMA controller automatically sets these bits to select the alternate channel control data

structure.

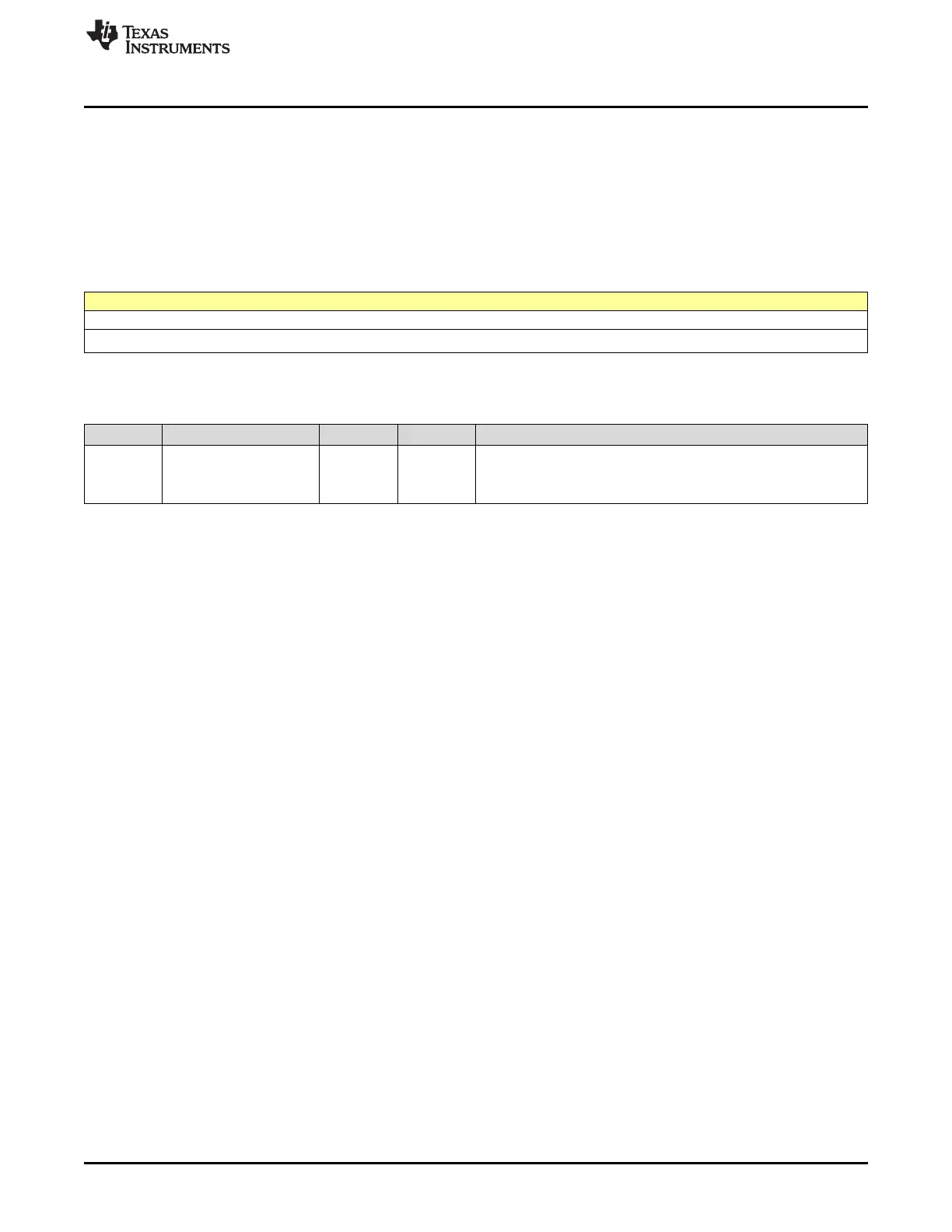

Figure 4-19. DMA_ALTSET Register

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

SET_n

W-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

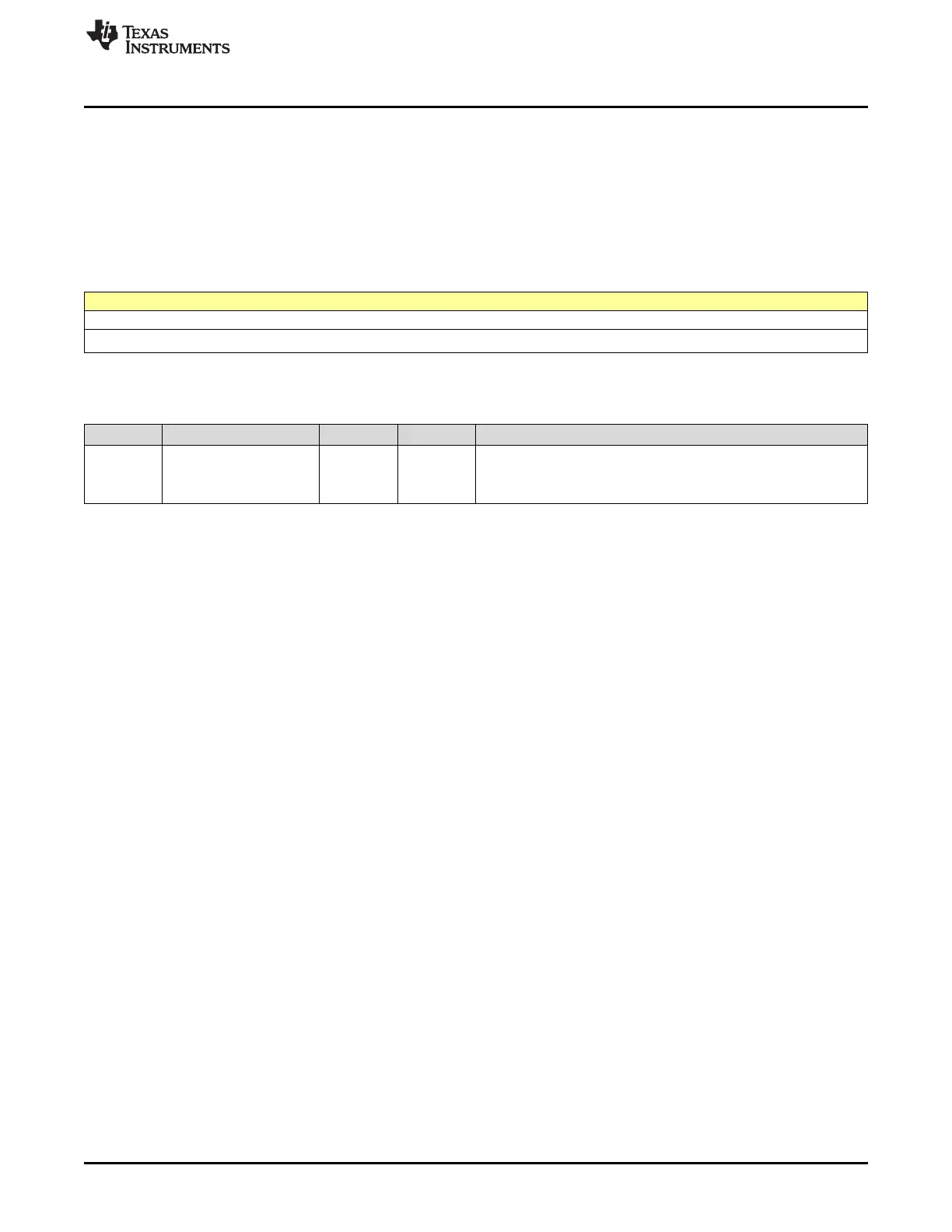

Table 4-23. DMA_ALTSET Register Field Descriptions

Bit Field Type Reset Description

31-0 SET_n W 0h

Channel [n] Alternate Set

0h = DMA channel [n] is using the primary control structure

1h = DMA channel [n] is using the alternate control structure

Loading...

Loading...