SD-HOST Registers

www.ti.com

388

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

SD Host Controller Interface

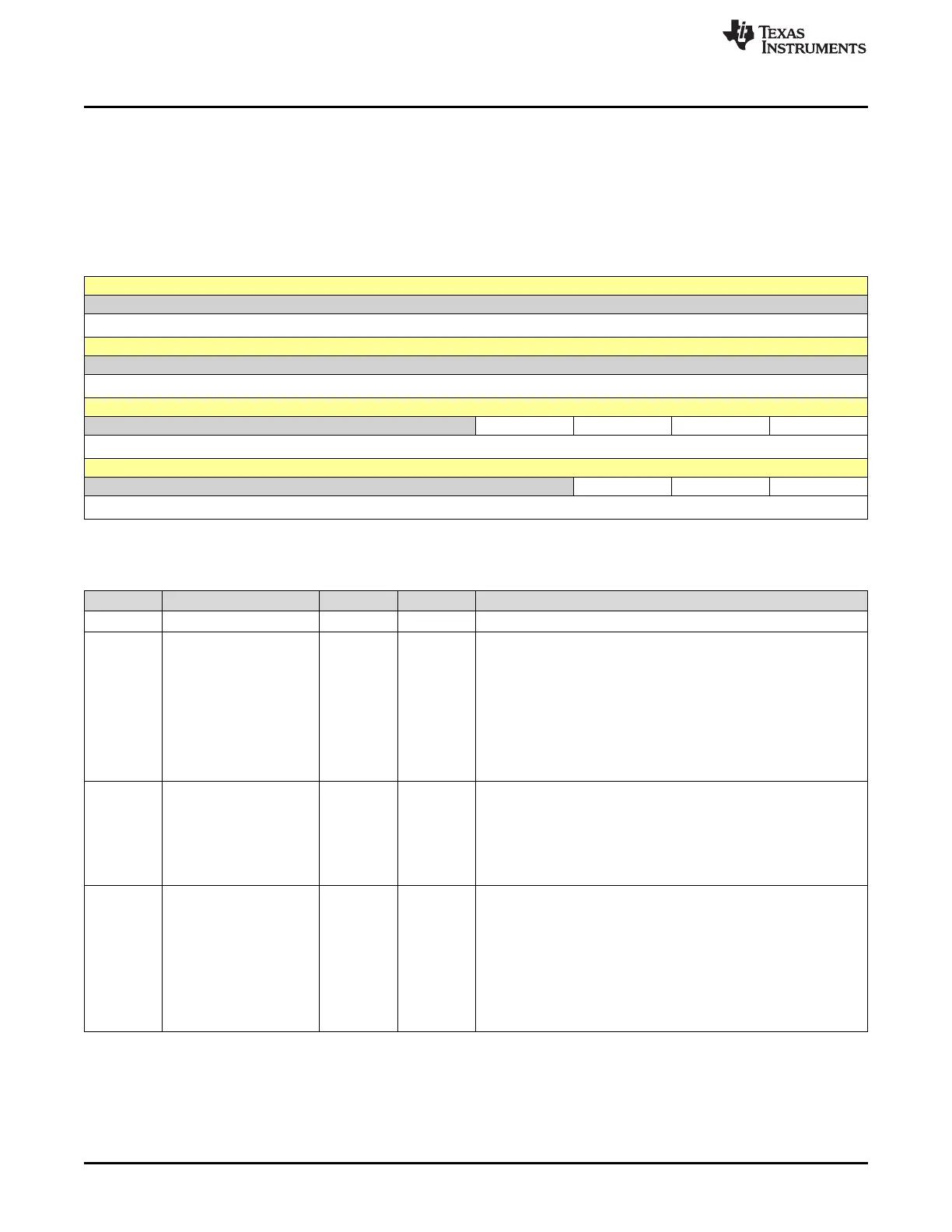

11.7.11 MMCHS_PSTATE Register (Offset = 224h) [reset = 0h]

Present State register

MMCHS_PSTATE is shown in Figure 11-12 and described in Table 11-15.

Return to Summary Table.

The host can get status of the host controller from this 32-bit read-only register.

Figure 11-12. MMCHS_PSTATE Register

31 30 29 28 27 26 25 24

RESERVED

R-0h

23 22 21 20 19 18 17 16

RESERVED

R-0h

15 14 13 12 11 10 9 8

RESERVED BRE BWE RTA WTA

R-0h R-0h R-0h R-0h R-0h

7 6 5 4 3 2 1 0

RESERVED DLA DAT1 CMDI

R-0h R-0h R-0h R-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

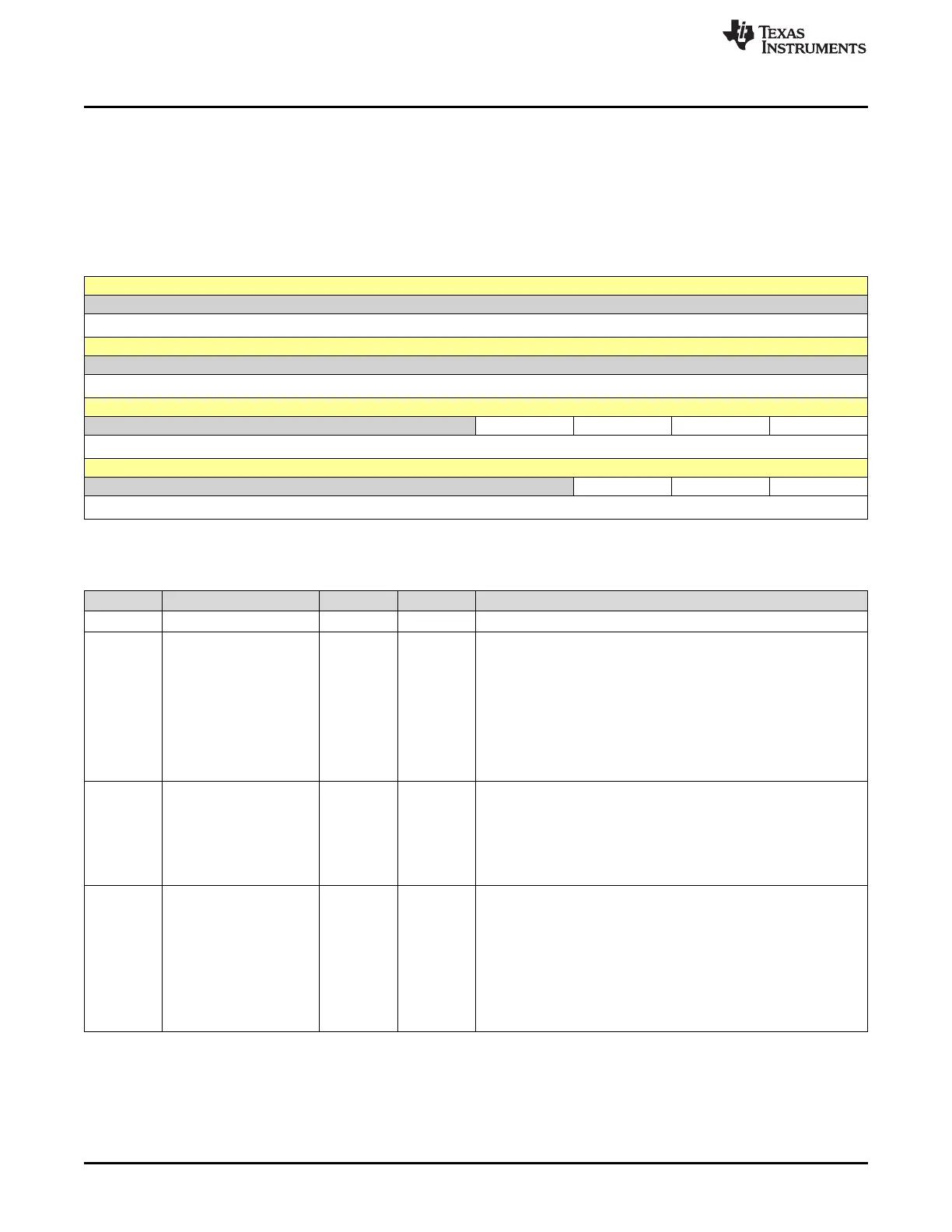

Table 11-15. MMCHS_PSTATE Register Field Descriptions

Bit Field Type Reset Description

31-12 RESERVED R 0h

11 BRE R 0h

Buffer read enable

This bit is used for non-DMA read transfers. It indicates that a

complete block specified by MMCi.MMCHS_BLK[10:0] BLEN bits

has been written in the buffer and is ready to be read.

It is set to 0 when the entire block is read from the buffer. It is set to

1 when a block data is ready in the buffer and generates the Buffer

read ready status of interrupt (MMCi.MMCHS_STAT[5] BRR bit).

0h = Read BLEN bytes disable

1h = Read BLEN bytes enable. Readable data exists in the buffer.

10 BWE R 0h

Buffer Write enable

This status is used for non-DMA write transfers. It indicates if space

is available for write data.

0h = There is no room left in the buffer to write BLEN bytes of data.

1h = There is enough space in the buffer to write BLEN bytes of

data.

9 RTA R 0h

Read transfer active

This status is used for detecting completion of a read transfer. It is

set to 1 after the end bit of read command or by activating a

continue request (MMCi.MMCHS_HCTL[17] CR bit) following a stop

at block gap request. This bit is set to 0 when all data have been

read by the local host after last block or after a stop at block gap

request.

0h = No valid data on the mmci_dat lines

1h = Read data transfer ongoing

Loading...

Loading...