www.ti.com

SHA-MD5 Registers

715

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

SHA/MD5 Accelerator

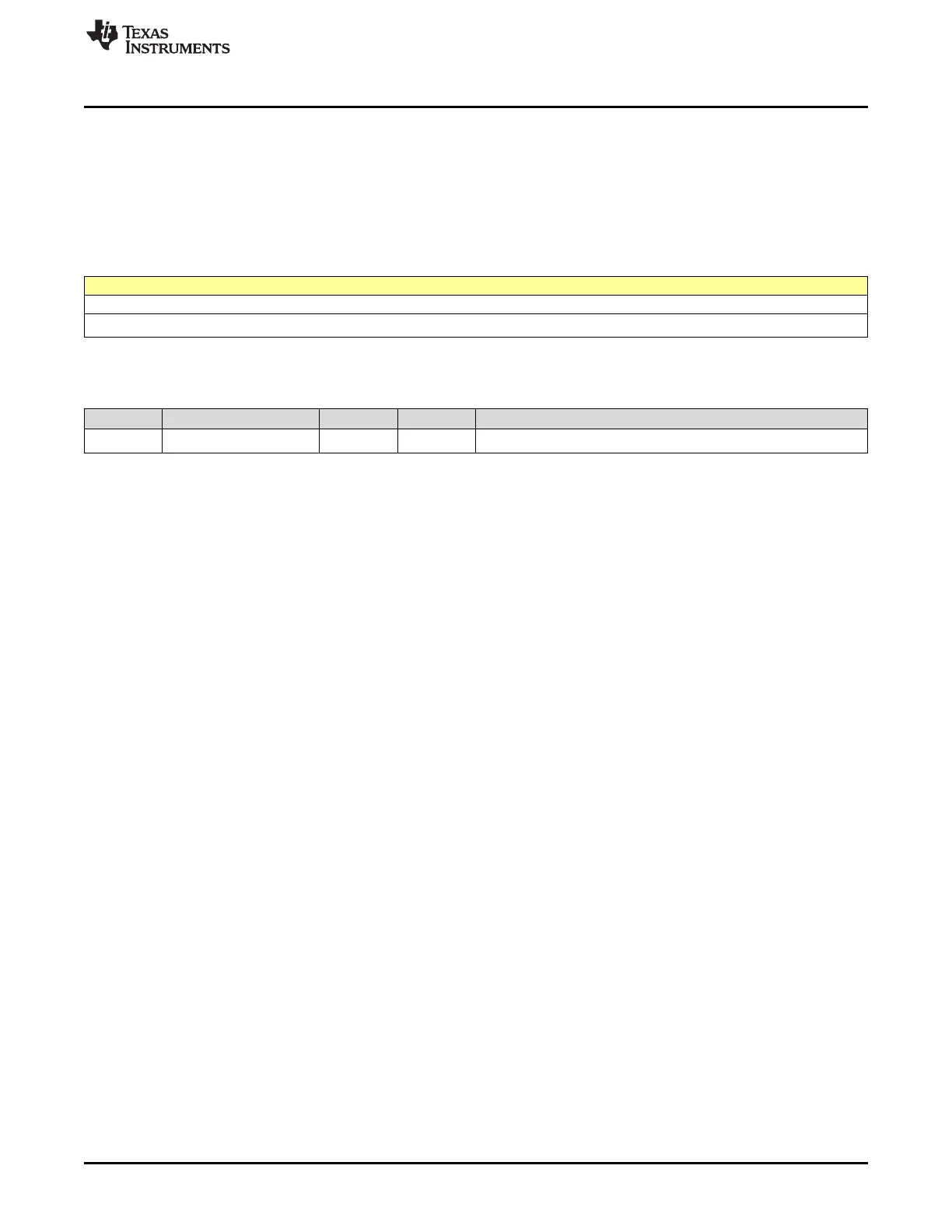

19.2.8 SHAMD5_ODIGEST_H Register (Offset = 1Ch) [reset = 0h]

SHAMD5_ODIGEST_H is shown in Figure 19-12 and described in Table 19-19.

Return to Summary Table.

WRITE: Outer Digest [31:0] for SHA-2 / HMAC Key [255:224] for HMAC key proc

READ: Outer Digest [31:0] for SHA-2

Figure 19-12. SHAMD5_ODIGEST_H Register

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

DATA

R/W-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

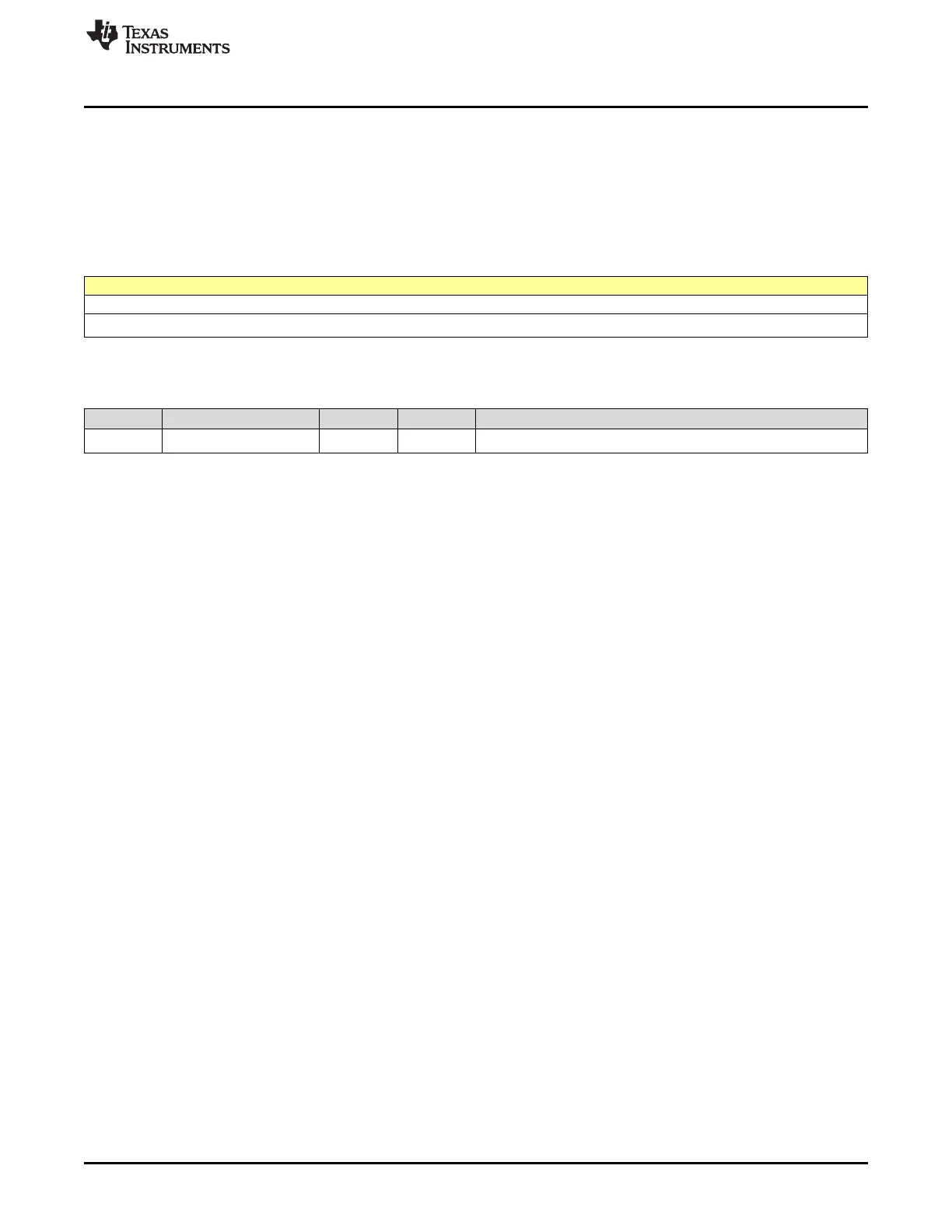

Table 19-19. SHAMD5_ODIGEST_H Register Field Descriptions

Bit Field Type Reset Description

31-0 DATA R/W 0h

Data

Inner digest registers: The following registers hold the inner digest for HMAC and hash operations:

• SHAMD5_IDIGEST_A

• SHAMD5_IDIGEST_B

• SHAMD5_IDIGEST_C

• SHAMD5_IDIGEST_D

• SHAMD5_IDIGEST_E

• SHAMD5_IDIGEST_F

• SHAMD5_IDIGEST_G

• SHAMD5_IDIGEST_H

The inner or initial digest for HMAC and hash continue (HMAC key processing = 0 and use algorithm

constants = 0) operations must be written to these registers before starting the operation by writing to

S_HASH_MODE. Only the relevant digest registers for the selected algorithm must be written, A-D for

MD5, A-E for SHA-1, A-H for SHA-2. When use algorithm constants is 1, these registers do need not to be

written, because they are overwritten with the appropriate algorithm constants.

For HMAC operations with key preprocessing enabled (HMAC key processing = 1), these registers must

be written with the upper 256 bits of the HMAC key, in little-endian format (first byte of key string in bits

[7:0]). If the HMAC key is less than 512 bits in size, it must be padded to the block size with zeroes on the

most significant bytes. All 16 HMAC key registers must be written explicitly, as the core does not pad the

HMAC key. Additionally, if the HMAC key is larger than 512 bits, the host is responsible for performing a

preprocessing step to reduce it to one 512-bit block. This involves hashing the large key and padding the

hash result with zeroes until it is 512 bits wide.

The (intermediate) result digest or MAC value can be read from these registers when the status register

indicates that the operation is done, or suspended due to a context switch request (reading at other times

results in all zeroes being returned). The MD5 result is available from digest registers A-D, the SHA-1

result from registers A-E, the SHA-224 final result from registers A-G, and the SHA-2 intermediate and

SHA-256 final result from registers A-H.

The order of the bytes within the digest can be fed back unmodified into the little-endian data input when

preprocessing HMAC keys larger than 64 bytes; or it can typically be inserted unmodified into a little-

endian data stream (such as IPSEC packets), regardless of the selected algorithm.

The HMAC key itself cannot be read back from these registers, but is preserved for future processing as

long as the SHAMD5_ODIGEST registers are not overwritten; this allows reuse of the HMAC key (without

having to redo the HMAC key processing) for subsequent data blocks without having to reload it. This is

done by setting HMAC key processing to 0 and Reuse HMAC key to 1 in the SHAMD5_MODE register.

Loading...

Loading...