SHA/MD5 Functional Description

www.ti.com

696

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

SHA/MD5 Accelerator

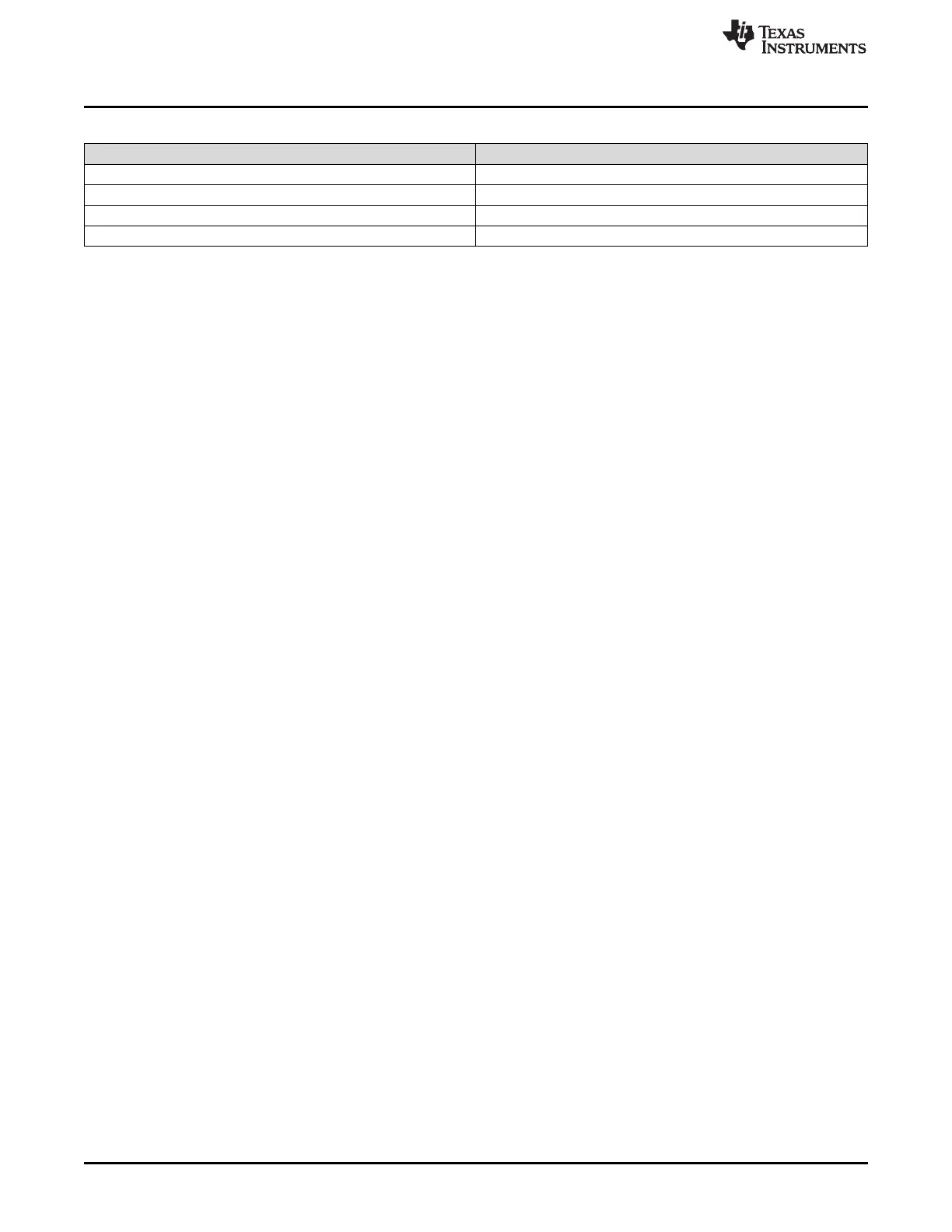

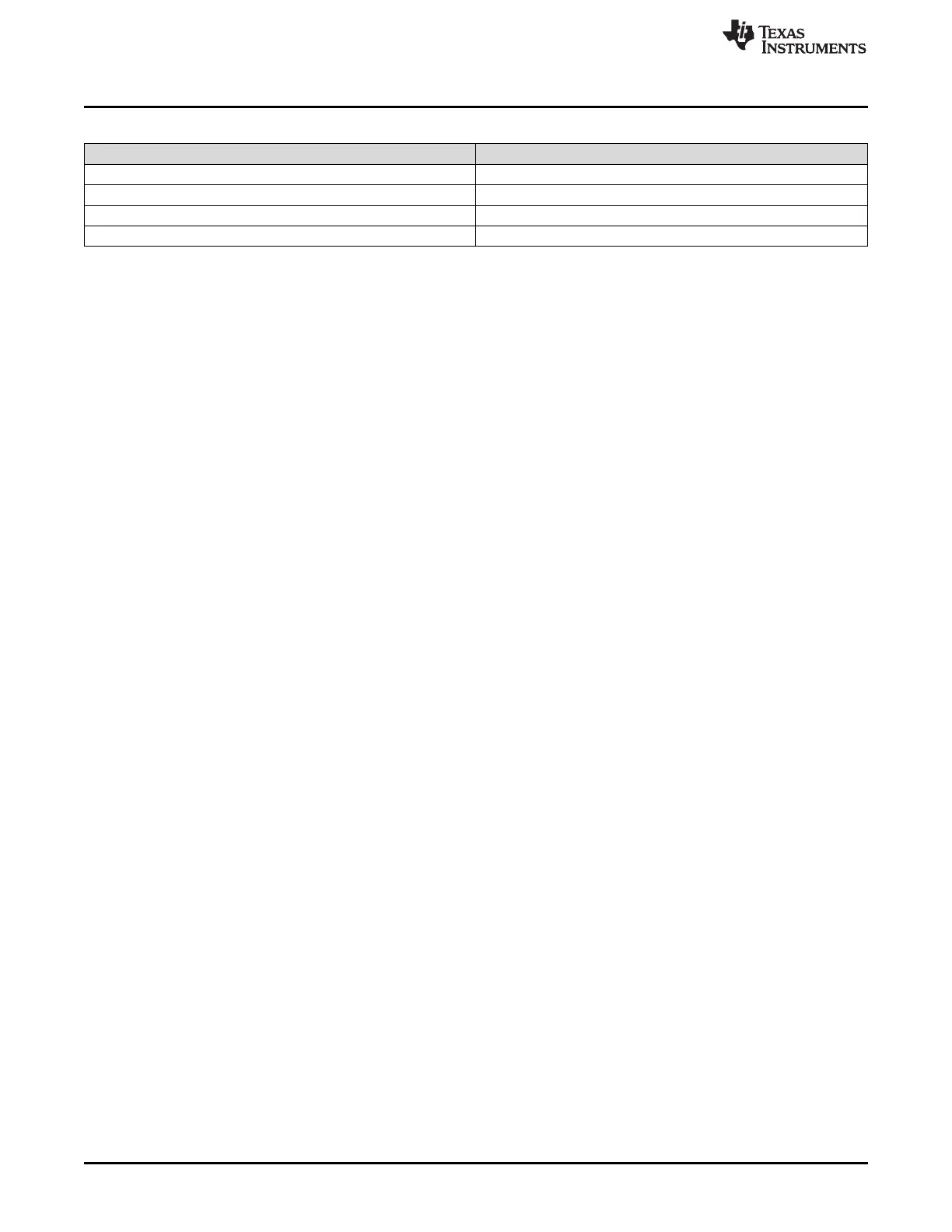

Table 19-2. SHA/MD5 Module Algorithm Selection

ALGO Field of SHAMD5_MODE Register Description

0x0 MD5 algorithm selected

0x1 SHA-1 algorithm selected

0x2 SHA-224 algorithm selected

0x3 SHA-256 algorithm selected

19.1.3.1 SHA Mode

19.1.3.1.1 Starting a New Hash

To start a new hash, follow these steps:

1. Set the ALGO bit field in the SHAMD5_MODE register to 0x1, 0x2, or 0x3 to select SHA-1, SHA-224,

or SHA-256, respectively.

2. Set the ALGO_CONSTANT bit in the SHAMD5_MODE register to 1 to initialize all SHA Inner/Outer

Digest n registers from SHAMD5_ODIGEST_A/SHAMD5_IDIGEST_A to

SHAMD5_ODIGEST_H/SHAMD5_IDIGEST_H with their default values specified by the algorithm, and

set the SHAMD5_DIGESTCOUNT register to 0.

3. Set the CLOSE_HASH bit of the SHA Mode (SHAMD5_MODE) register to let the SHA engine do the

padding. If the hash is computed in one shot, the length of the message can be any value up to

128MB. To process an intermediate hash digest, the CLOSE_HASH bit is set to 0, in which case the

packets hashed must be 64 bytes; the last packet must be hashed with the CLOSE_HASH bit set to 1.

4. Specify the LENGTH field in the SHA Length (SHAMD5_LENGTH) register of the hash data to process

in bytes.

When the configuration is complete, the INPUT_READY status bit equals 1 in the SHA Interrupt Status

(SHAMD5_IRQSTATUS) register (regardless of whether or not the M_INPUT_READY bit in the

SHAMD5_IRQENABLE register is set). When this bit is set, it indicates the SHA engine can receive the

data to process. Data must be written to the 16 × 32-bit SHAMD5_DATA_n_IN registers that provide

storage for one 64-byte block of data. Unless the CLOSE_HASH bit is set, all of the

SHAMD5_DATA_n_IN input buffers must be filled. Data can be written by single write accesses to the 16

registers from a processor or by a DMA transfer.

For µDMA transfers, the PDMA_EN bit must be set in the SHAMD5_SYSCONFIG register, and the

appropriate mask bits must be set in the SHAMD5_DMAIM register before starting the new hash. If the

µDMA is used for transfers, the SHAMD5_IRQENABLE register should be clear so all interrupts are

generated through the µDMA interrupt registers.

The µDMA must be configured to transfer 16 data words of 32 bits each time it is triggered by a µDMA

request from the SHA/MD5 module. The 16 data words written are sent to the 16 SHAMD5_DATA_n_IN

registers.

The module detects that a 64-byte block is available, then moves the data to a working register space for

processing and asserts the INPUT_READY bit in the SHAMD5_IRQSTATUS register to 1. If the

PDMA_EN bit in the SHAMD5_SYSCONFIG register has been set to 1, a new µDMA request triggers a

new block transfer; otherwise, the processor polls the INPUT_READY bit and writes the 16 data words of

32 bits when it equals 1.

This operation is repeated until the length of the message to hash is reached. The OUPUT_READY bit in

the SHAMD5_IRQSTATUS register then indicates that the hash operation is complete. If the PIT_EN bit in

the SHAMD5_SYSCONFIG register is set, an interrupt (active low) is also generated to indicate the hash

completion.

The processor can then read the eight digest registers A to H that contain the hash or HMAC result. If the

hash is an intermediate result of a larger hash, the digest count register must also be read and saved. See

Table 19-3 and Table 19-4.

Loading...

Loading...