Timer Registers

www.ti.com

346

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

General-Purpose Timers

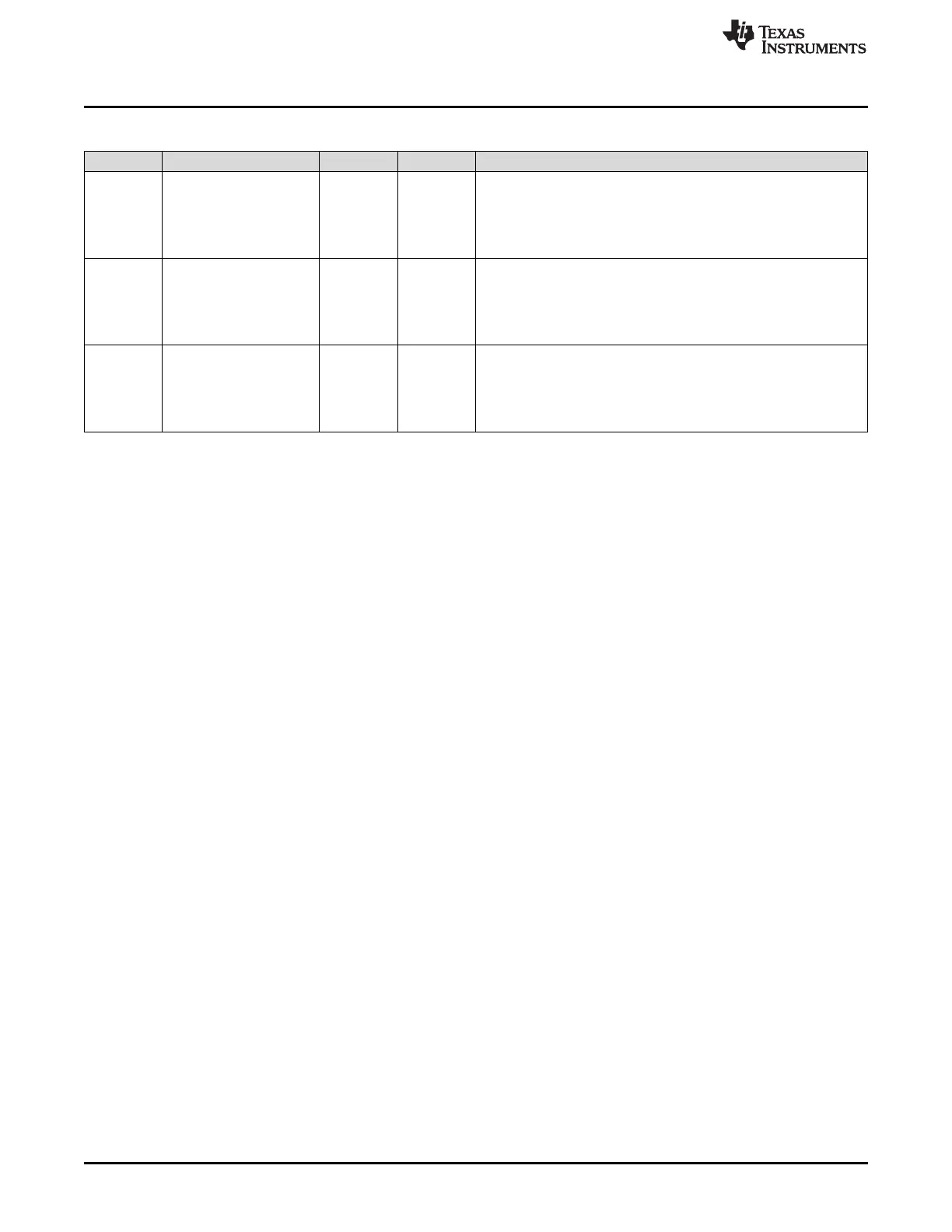

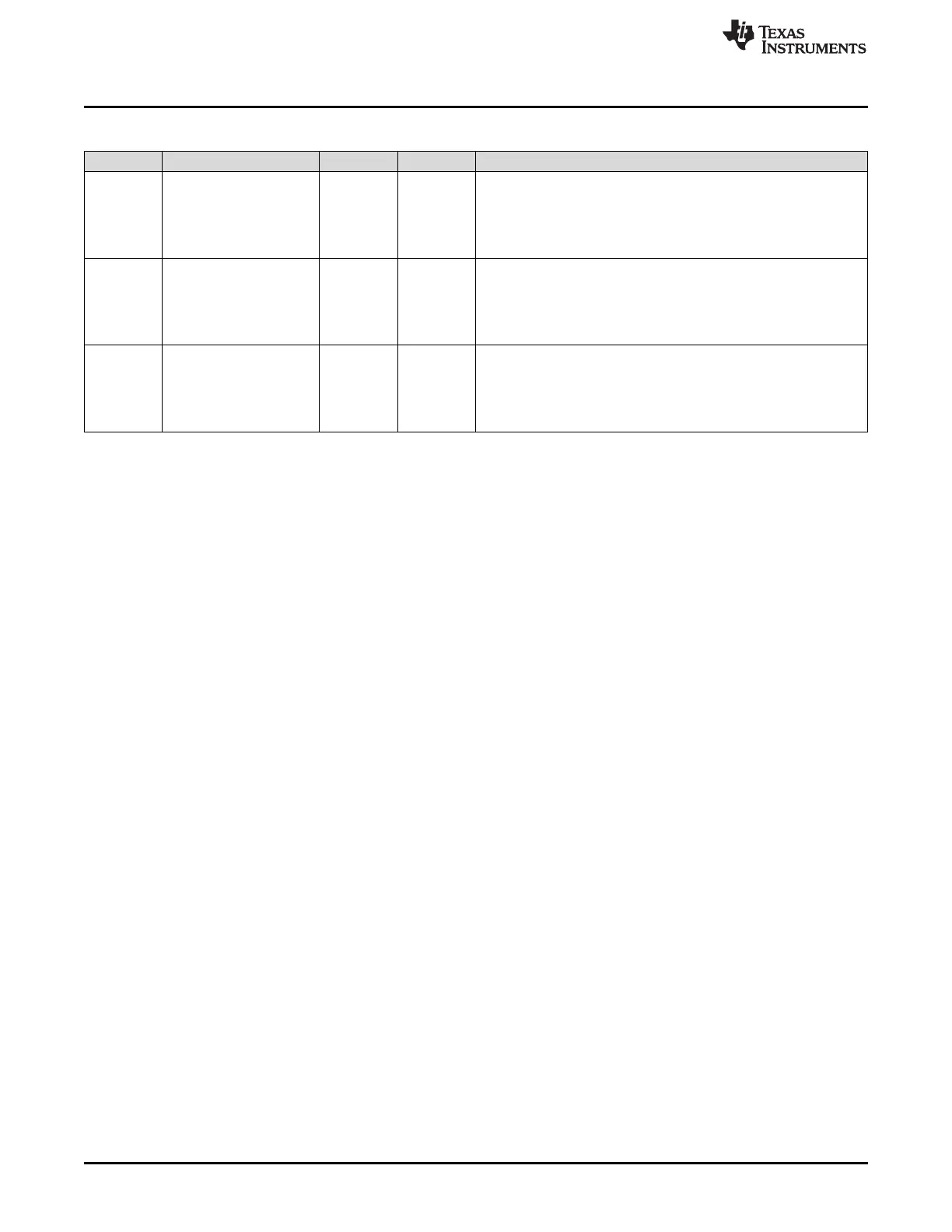

Table 9-29. GPTMDMAEV Register Field Descriptions (continued)

Bit Field Type Reset Description

2 CAEDMAEN R/W 0h

GPTM A Capture Event DMA Trigger Enable. When this bit is

enabled, a Timer A dma_req signal is sent to the DMA when a

capture event has occurred.

0h = Timer A capture event DMA trigger is disabled.

1h = Timer A capture event DMA trigger is enabled.

1 CAMDMAEN R/W 0h

GPTM A Capture Match Event DMA Trigger Enable. When this bit is

enabled, a Timer A dma_req signal is sent to the DMA when a

capture match event has occurred.

0h = Timer A capture match DMA trigger is disabled.

1h = Timer A capture match DMA trigger is enabled.

0 TATODMAEN R/W 0h

GPTM A Time-Out Event DMA Trigger Enable. When this bit is

enabled, a Timer A dma_req signal is sent to the DMA on a time-out

event.

0h = Timer A time-out DMA trigger is disabled.

1h = Timer A time-out DMA trigger is enabled.

Loading...

Loading...