SHA/MD5 Functional Description

www.ti.com

694

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

SHA/MD5 Accelerator

19.1 SHA/MD5 Functional Description

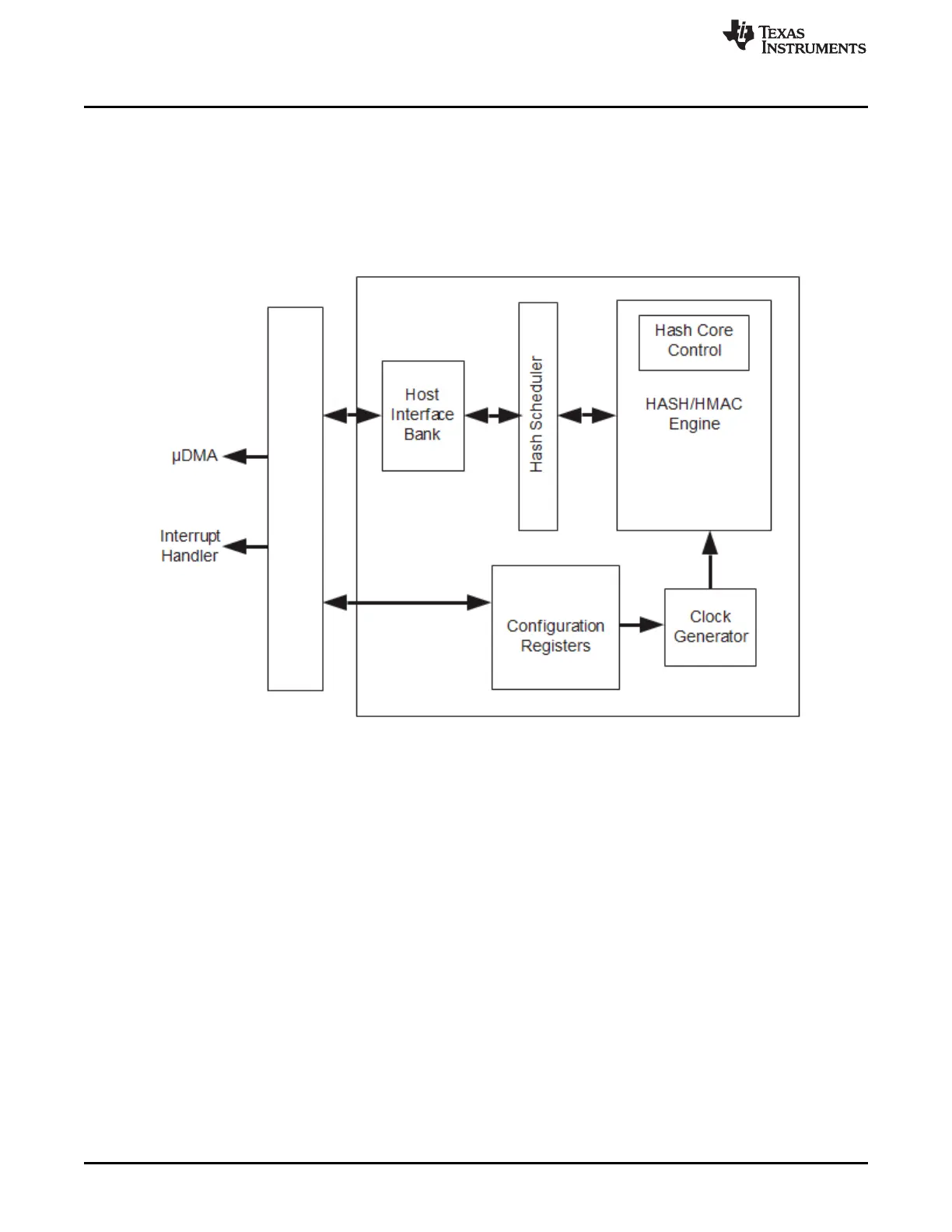

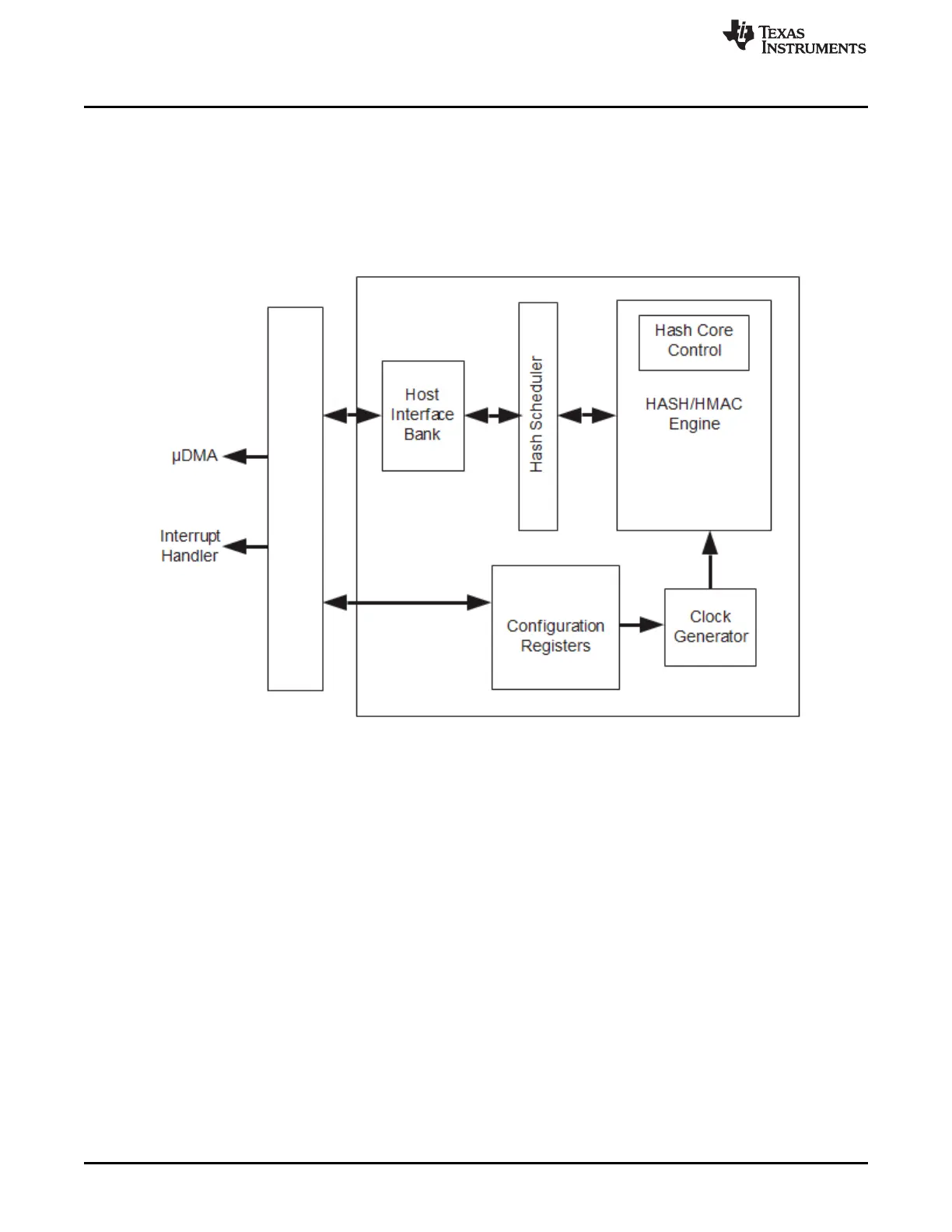

19.1.1 SHA/MD5 Block Diagram

Figure 19-1 shows the module architecture, which consists of four primary blocks: the hash/HMAC engine,

the configuration registers, and the interface to the µDMA and the interrupt handler.

Figure 19-1. SHA/MD5 Module Block Diagram

19.1.1.1 Configuration Registers

The configuration registers contain the following global control and status registers for the SHA/MD5

module:

• A system control register that controls the mode of operation (SHAMD5_SYSCONFIG register)

• µDMA interrupt control registers (DTHE_SHA_IM, DTHE_SHA_RIS, DTHE_SHA_MIS, and

DTHE_SHA_IC registers, which reside in the Encryption Control Base address space)

• An interrupt status register (SHAMD5_IRQSTATUS register)

• An enable register (SHAMD5_IRQENABLE register)

19.1.1.2 Hash/HMAC Engine

The Hash/HMAC engine performs the SHA-1, SHA-2, or MD5 hash computation. When loaded with a data

block, and optionally an intermediate digest, it independently performs the hash computation (64 or 80

rounds, depending on the algorithm) on that data block.

The engine can also start from the specified initial digest values instead of a loaded intermediate.

Furthermore, it can perform the IPAD and OPAD XORs for MAC operations. The hash core does not

perform any hash padding; this is performed in the host interface block, where the data input registers are

located. A loaded data block must always be a full 64 bytes (512 bits) long.

Loading...

Loading...