SPI Registers

www.ti.com

304

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

SPI (Serial Peripheral Interface)

8.6.11 SPI_XFERLEVEL Register (offset = 17Ch) [reset = 0h]

SPI_XFERLEVEL is shown in Figure 8-30 and described in Table 8-17.

This register provides the transfer levels required to use the FIFO buffer during transfer.

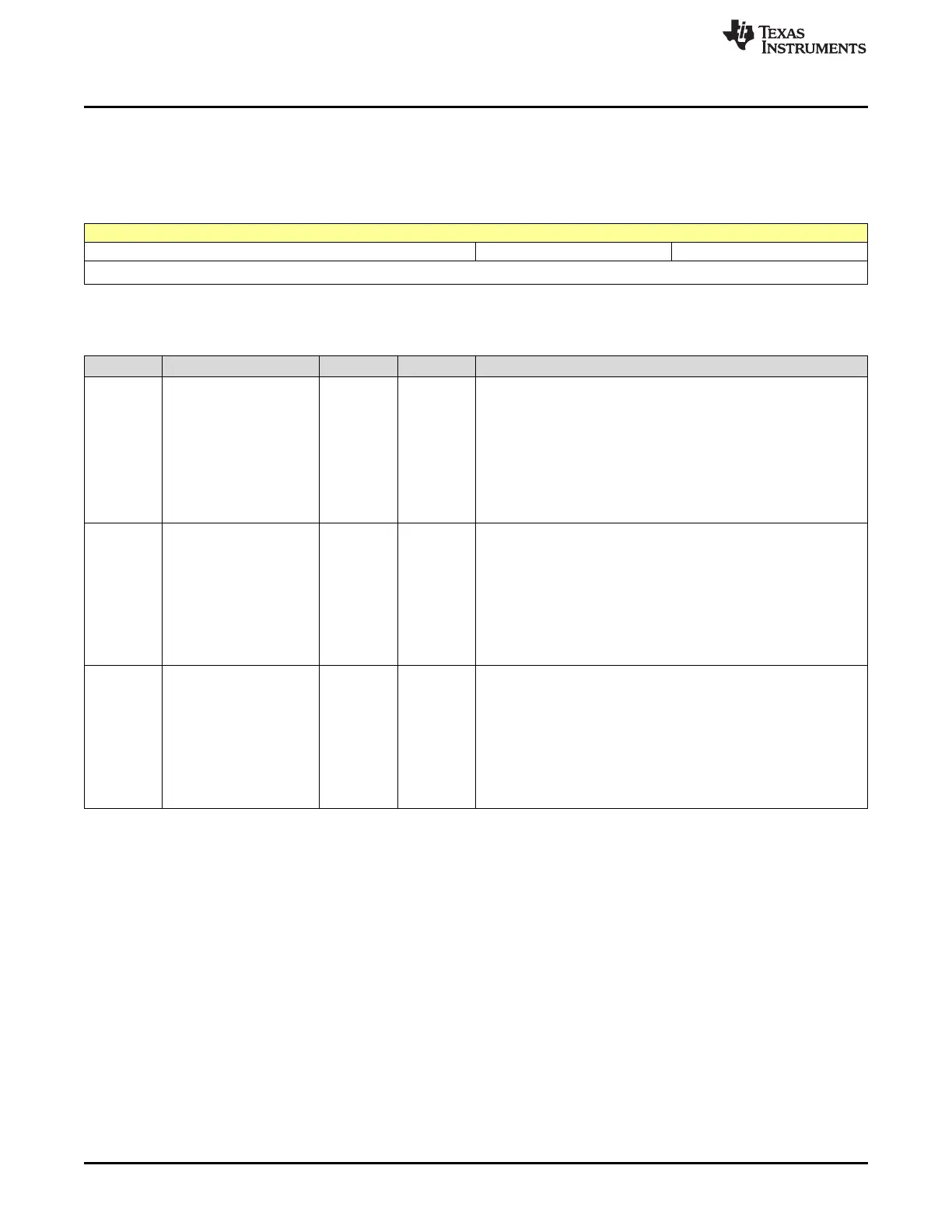

Figure 8-30. SPI_XFERLEVEL Register

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

WCNT AFL AEL

R/W-0h R/W-0h R/W-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

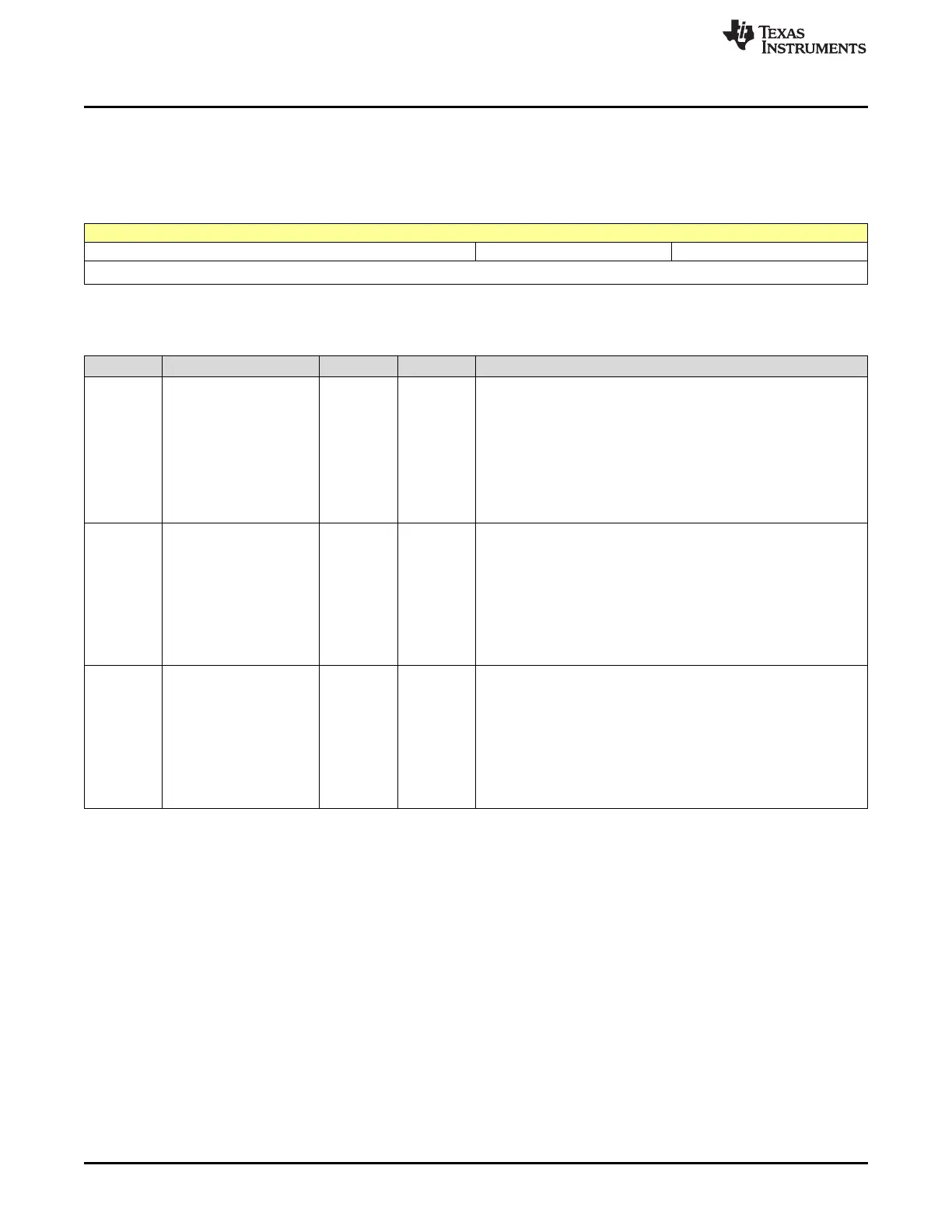

Table 8-17. SPI_XFERLEVEL Register Field Descriptions

Bit Field Type Reset Description

31-16 WCNT R/W 0h SPI word counter.

This register holds the programmable value of the number of SPI

words to be transferred on the channel using the FIFO buffer.

When the transfer starts, a read back in this register returns the

current SPI word transfer index.

0h = Counter not used

1h = One SPI word

FFFEh = 65534 SPI word

FFFFh = 65535 SPI word

15-8 AFL R/W 0h Buffer almost full.

This register holds the programmable almost-full level value used to

determine almost-full buffer condition.

If the user wants an interrupt or a DMA read request to be issued

during a receive operation when the data buffer holds at least n

bytes, then the buffer SPI_XFERLEVEL[AFL] must be set with n-1.

0h = 1 byte

1h = 2 bytes

Fh = 16 bytes

7-0 AEL R/W 0h Buffer almost empty.

This register holds the programmable almost-empty level value used

to determine almost-empty buffer condition.

If the user wants an interrupt or a DMA write request to be issued

during a transmit operation when the data buffer is able to receive n

bytes, then the buffer SPI_XFERLEVEL[AEL] must be set with n-1.

0h = 1 byte

1h = 2 bytes

Fh = 16 bytes

Loading...

Loading...