www.ti.com

WATCHDOG Registers

351

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

Watchdog Timer

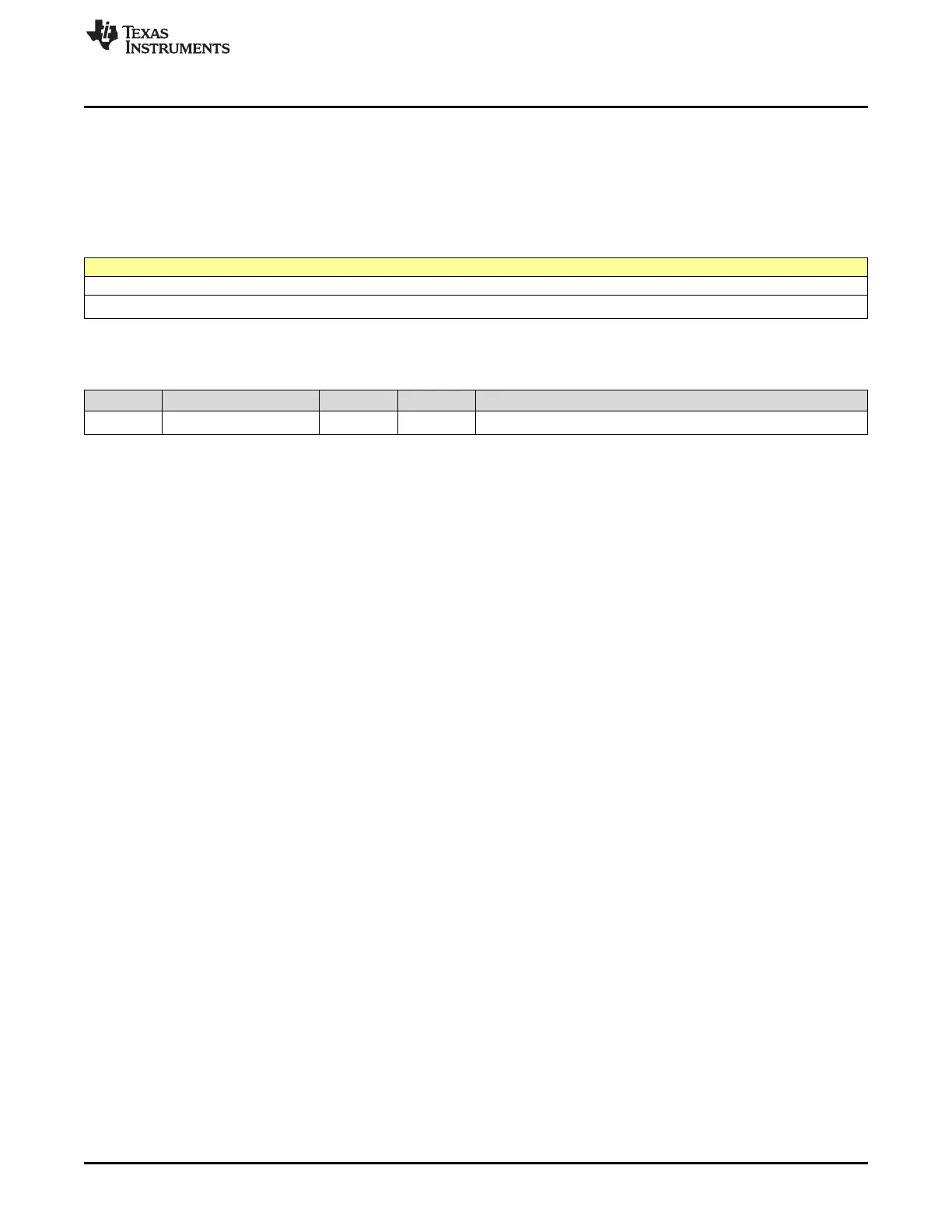

10.3.1 WDTLOAD Register (offset = 0h) [reset = FFFFFFFFh]

WDTLOAD is shown in Figure 10-2 and described in Table 10-2.

This register is the 32-bit interval value used by the 32-bit counter. When this register is written, the value

is immediately loaded and the counter restarts counting down from the new value. If the WDTLOAD

register is loaded with 0x0000.0000, an interrupt is immediately generated.

Figure 10-2. WDTLOAD Register

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

WDTLOAD

R/W-FFFFFFFFh

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

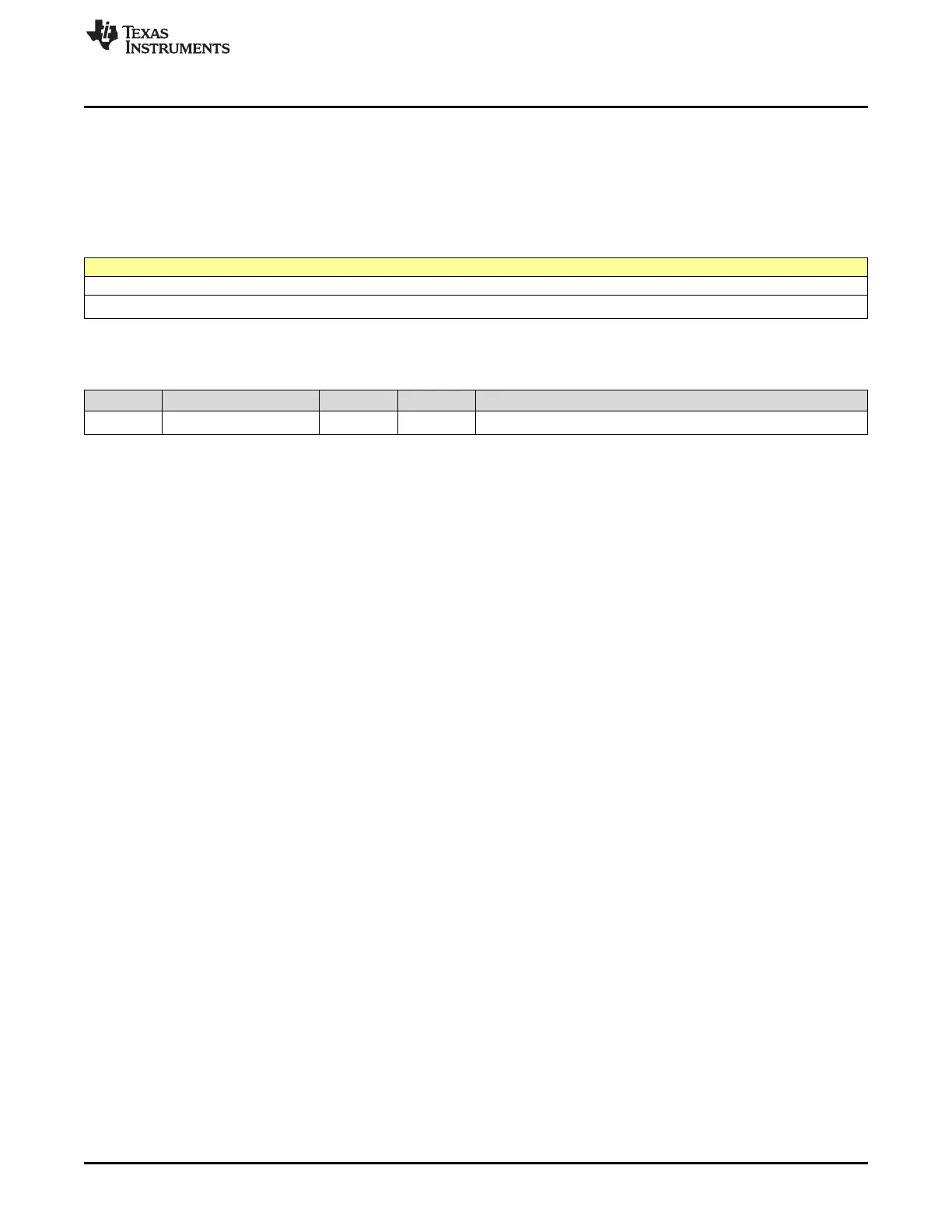

Table 10-2. WDTLOAD Register Field Descriptions

Bit Field Type Reset Description

31-0 WDTLOAD R/W FFFFFFFFh

Watchdog Load Value

Loading...

Loading...