www.ti.com

Functional Description

55

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

Cortex

®

-M4 Processor

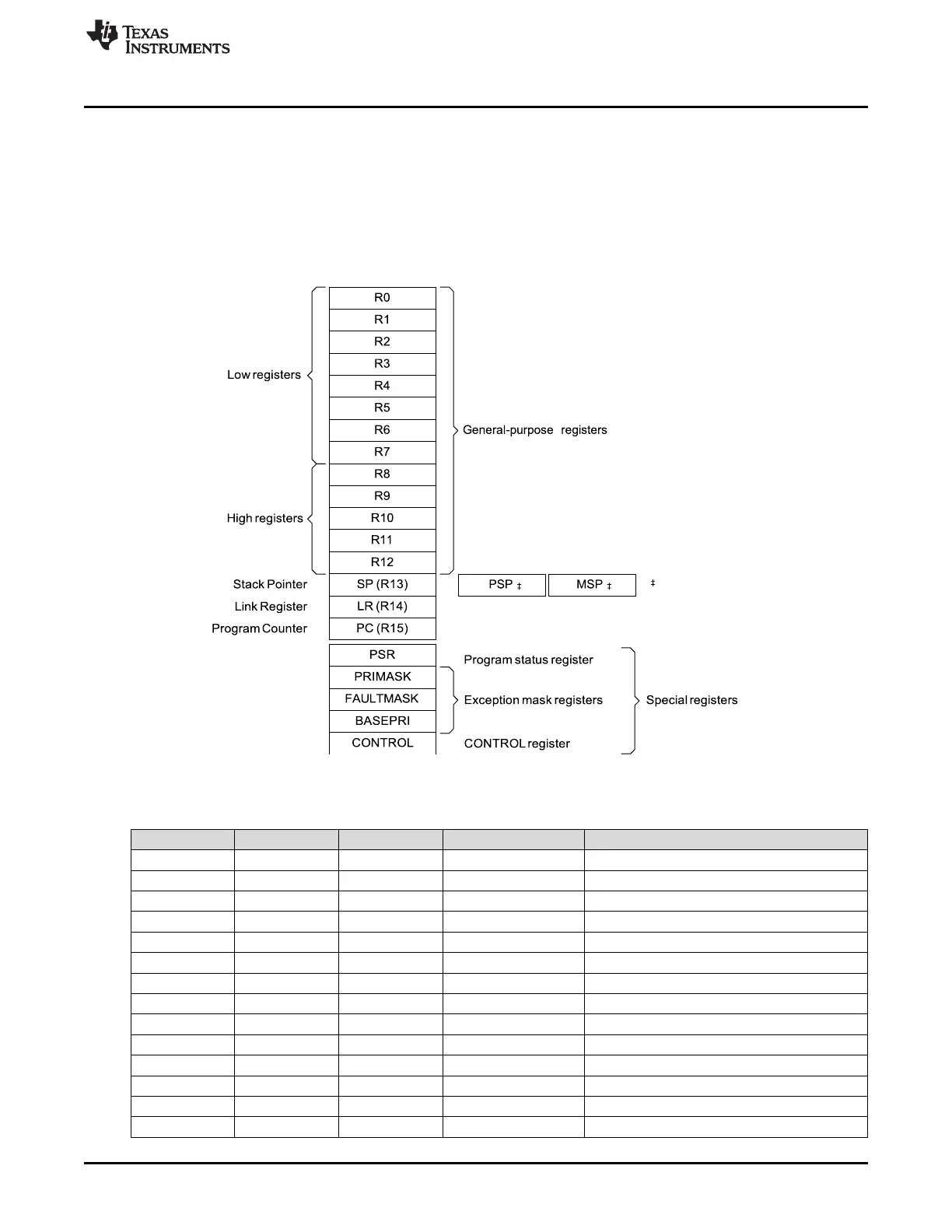

2.2.2 Register Description

2.2.2.1 Register Map

Figure 2-2 shows the Cortex

®

-M4 register set. Table 2-2 lists the core registers. The core registers are not

memory-mapped and are accessed by register name, so the base address is n/a (not applicable) and

there is no offset.

Figure 2-3. Cortex

®

-M4 Register Set

Table 2-2. Processor Register Map

Offset Name Type Reset Description

– R0 R/W – Cortex General-Purpose register 0

– R1 R/W – Cortex General-Purpose register 1

– R2 R/W – Cortex General-Purpose register 2

– R3 R/W – Cortex General-Purpose register 3

– R4 R/W – Cortex General-Purpose register 4

– R5 R/W – Cortex General-Purpose register 5

– R6 R/W – Cortex General-Purpose register 6

– R7 R/W – Cortex General-Purpose register 7

– R8 R/W – Cortex General-Purpose register 8

– R9 R/W – Cortex General-Purpose register 9

– R10 R/W – Cortex General-Purpose register 10

– R11 R/W – Cortex General-Purpose register 11

– R12 R/W – Cortex General-Purpose register 12

– SP R/W – Stack pointer

Loading...

Loading...