Register Map

www.ti.com

110

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

Cortex

®

-M4 Peripherals

3.3.1.21 FAULTSTAT Register (Offset = D28h) [reset = 0h]

FAULTSTAT is shown in Figure 3-21 and described in Table 3-24.

Return to Summary Table.

The FAULTSTAT register indicates the cause of a memory management fault, bus fault, or usage fault.

Each of these functions is assigned to a subregister as follows:

• Usage Fault Status (UFAULTSTAT), bits 31:16

• Bus Fault Status (BFAULTSTAT), bits 15:8

• Memory Management Fault Status (MFAULTSTAT), bits 7:0 (Not applicable for CC32xx)

FAULTSTAT is byte-accessible.

FAULTSTAT or its subregisters can be accessed as follows:

• The complete FAULTSTAT register, with a word access to offset 0xD28

• The MFAULTSTAT, with a byte access to offset 0xD28

• The MFAULTSTAT and BFAULTSTAT, with a halfword access to offset 0xD28

• The BFAULTSTAT, with a byte access to offset 0xD29

• The UFAULTSTAT, with a halfword access to offset 0xD2A

Bits are cleared by writing a 1 to them.

In a fault handler, the true faulting address can be determined by:

1. Read and save the Memory Management Fault Address (MMADDR) or Bus Fault Address

(FAULTADDR) value.

2. Read the MMARV bit in MFAULTSTAT, or the BFARV bit in BFAULTSTAT to determine if the

MMADDR or FAULTADDR contents are valid.

Software must follow this sequence because another higher priority exception might change the MMADDR

or FAULTADDR value. For example, if a higher priority handler preempts the current fault handler, the

other fault might change the MMADDR or FAULTADDR value.

NOTE: This register can only be accessed from privileged mode.

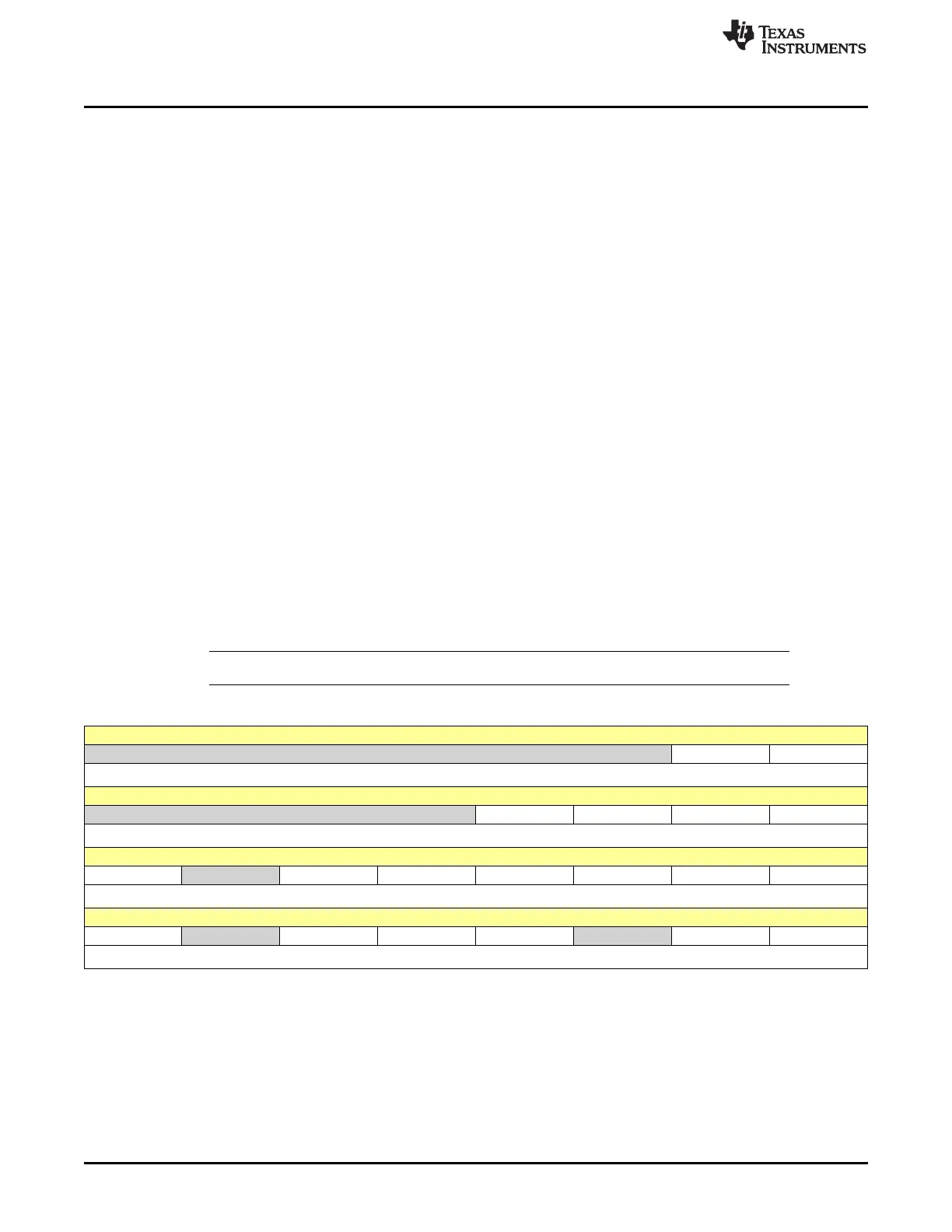

Figure 3-21. FAULTSTAT Register

31 30 29 28 27 26 25 24

RESERVED DIV0 UNALIGN

R-0h R/W1C-0h R/W1C-0h

23 22 21 20 19 18 17 16

RESERVED NOCP INVPC INVSTAT UNDEF

R-0h R/W1C-0h R/W1C-0h R/W1C-0h R/W1C-0h

15 14 13 12 11 10 9 8

BFARV RESERVED BLSPERR BSTKE BUSTKE IMPRE PRECISE IBUS

R/W1C-0h R-0h R/W1C-0h R/W1C-0h R/W1C-0h R/W1C-0h R/W1C-0h R/W1C-0h

7 6 5 4 3 2 1 0

MMARV RESERVED MLSPERR MSTKE MUSTKE RESERVED DERR IERR

R/W1C-0h R-0h R/W1C-0h R/W1C-0h R/W1C-0h R-0h R/W1C-0h R/W1C-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

Loading...

Loading...