I2C Registers

www.ti.com

222

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

Inter-Integrated Circuit (I

2

C) Interface

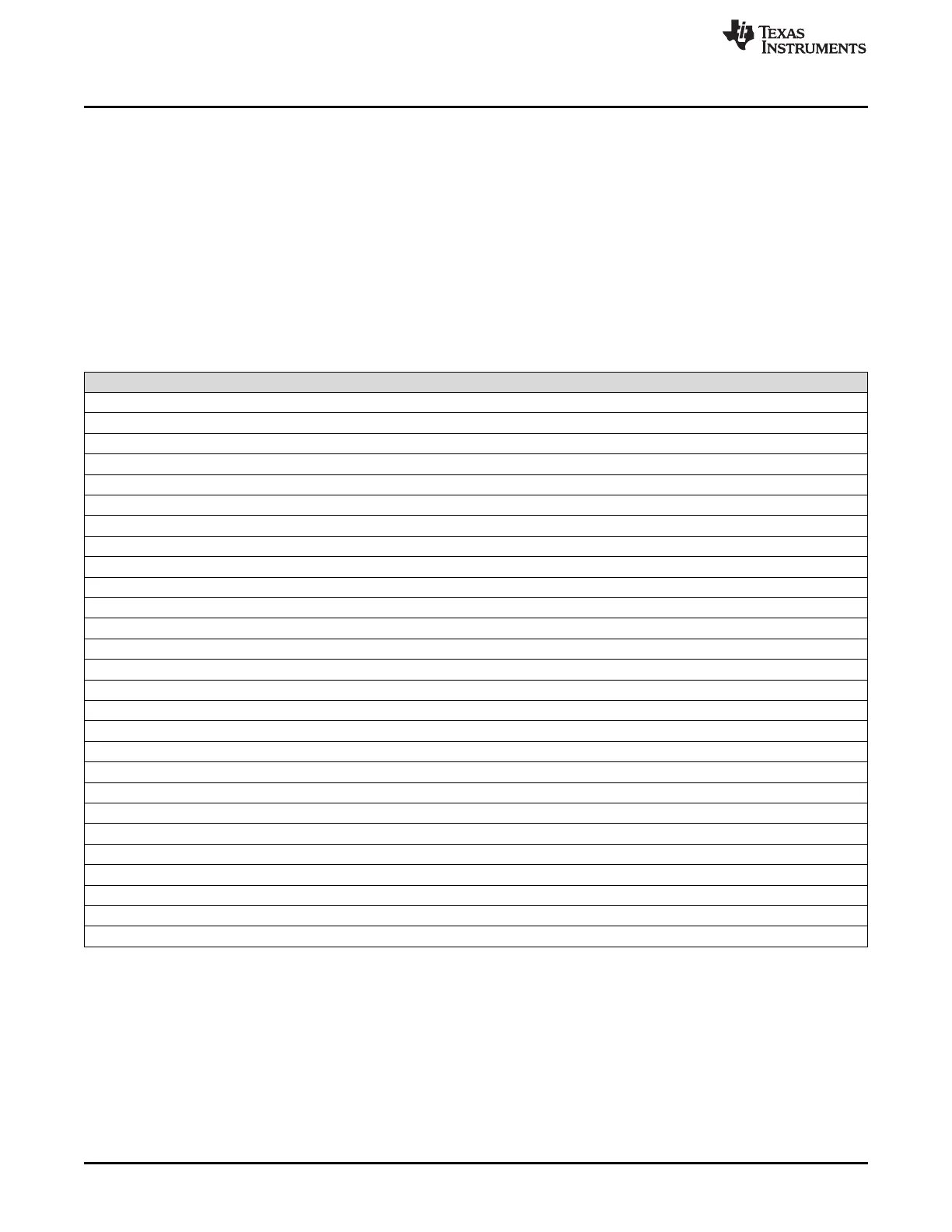

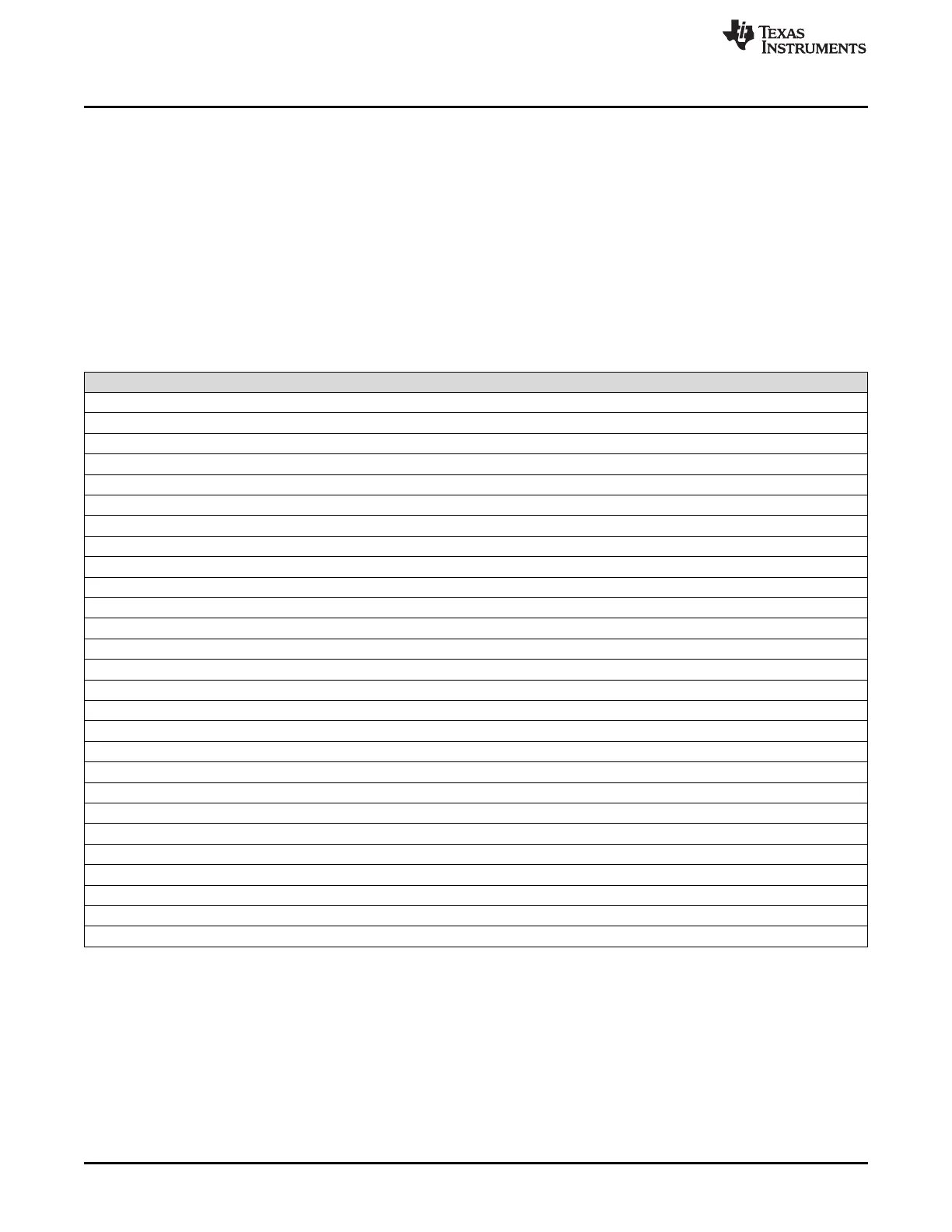

7.3 I2C Registers

Table 7-3 lists the memory-mapped registers for the I2C. All register offset addresses not listed in Table 7-

3 should be considered as reserved locations and the register contents should not be modified.

All addresses given are relative to the I2C base address: 0x4002.0000.

The I2C module clock must be enabled before the registers can be programmed. There must be a delay

of three system clocks after the I2C module clock is enabled before any I2C module registers are

accessed.

The hw_i2c.h file in the TivaWare Driver Library uses a base address of 0x800 for the I2C slave registers.

Be aware when using registers with offsets from 0x800 to 0x818 that TivaWare for E Series uses an offset

from 0x000 to 0x018 with the slave base address.

Table 7-3. I2C Registers

Offset Acronym Register Name Section

0h I2CMSA I2C Master Slave Address Section 7.3.1

4h I2CMCS I2C Master Control/Status Section 7.3.2

8h I2CMDR I2C Master Data Section 7.3.3

Ch I2CMTPR I2C Master Timer Period Section 7.3.4

10h I2CMIMR I2C Master Interrupt Mask Section 7.3.5

14h I2CMRIS I2C Master Control/Status Section 7.3.6

18h I2CMMIS I2C Master Masked Interrupt Status Section 7.3.7

1Ch I2CMICR I2C Master Interrupt Clear Section 7.3.8

20h I2CMCR I2C Master Configuration Section 7.3.9

24h I2CMCLKOCNT I2C Master Clock Low Timeout Count Section 7.3.10

2Ch I2CMBMON I2C Master Bus Monitor Section 7.3.11

30h I2CMBLEN I2C Master Burst Length Section 7.3.12

34h I2CMBCNT I2C Master Burst Count Section 7.3.13

800h I2CSOAR I2C Slave Own Address Section 7.3.14

804h I2CSCSR I2C Slave Control/Status Section 7.3.15

808h I2CSDR I2C Slave Data Section 7.3.16

80Ch I2CSIMR I2C Slave Interrupt Mask Section 7.3.17

810h I2CSRIS I2C Slave Raw Interrupt Status Section 7.3.18

814h I2CSMIS I2C Slave Masked Interrupt Status Section 7.3.19

818h I2CSICR I2C Slave Interrupt Clear Section 7.3.20

81Ch I2CSOAR2 I2C Slave Own Address 2 Section 7.3.21

820h I2CSACKCTL I2C Slave ACK Control Section 7.3.22

F00h I2CFIFODATA I2C FIFO Data Section 7.3.23

F04h I2CFIFOCTL I2C FIFO Control Section 7.3.24

F08h I2CFIFOSTATUS I2C FIFO Status Section 7.3.25

FC0h I2CPP I2C Peripheral Properties Section 7.3.26

FC4h I2CPC I2C Peripheral Configuration Section 7.3.27

Loading...

Loading...